Modeling of Thermal Noise Effects in Nanoscale Circuits and Design of Noise Tolerant Circuits

Designers need new tools to simulate logic circuits in the presence of noise. Time-domain analysis helps understand how transient faults affect a circuit and can guide designers in producing noise-resistant circuitry. However, standard approaches such as SPICE that can be used to model intrinsic noise sources in the time domain are computationally expensive. Moreover, small noise-driven fluctuations in electron occupation of circuit nodes introduce time-varying biasing point fluctuations, increasing the modeling complexity.

To address these challenges, we have proposed a new approach to modeling thermal noise and random telegraph signal (RTS) noise directly in the time domain by developing and solving a series of stochastic differential equations (SDEs). In comparisons to traditional SPICE-based simulations, our approach can provide 3 orders of magnitude speedup in simulation time without sacrificing accuracy.

Moreover, we have also introduced a novel, iterative threshold-crossing algorithm, aimed at the efficient sampling of rare noise transients. We have shown that Monte-Carlo simulations based on this approach can detect rare high-amplitude single event transients (SETs) that would be impossible to uncover with standard SPICE-based transient simulators.

To address these challenges, we have proposed a new approach to modeling thermal noise and random telegraph signal (RTS) noise directly in the time domain by developing and solving a series of stochastic differential equations (SDEs). In comparisons to traditional SPICE-based simulations, our approach can provide 3 orders of magnitude speedup in simulation time without sacrificing accuracy.

Moreover, we have also introduced a novel, iterative threshold-crossing algorithm, aimed at the efficient sampling of rare noise transients. We have shown that Monte-Carlo simulations based on this approach can detect rare high-amplitude single event transients (SETs) that would be impossible to uncover with standard SPICE-based transient simulators.

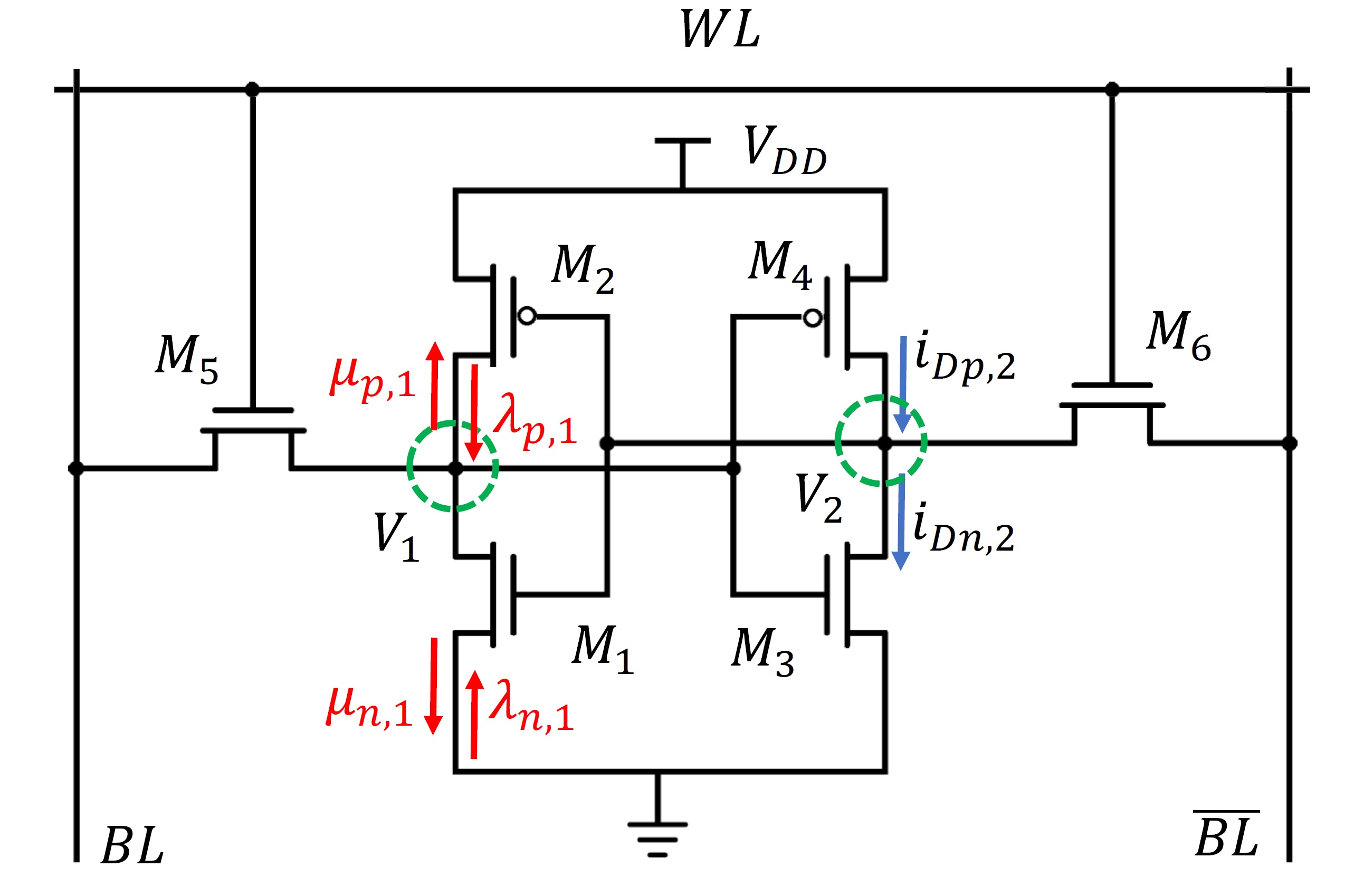

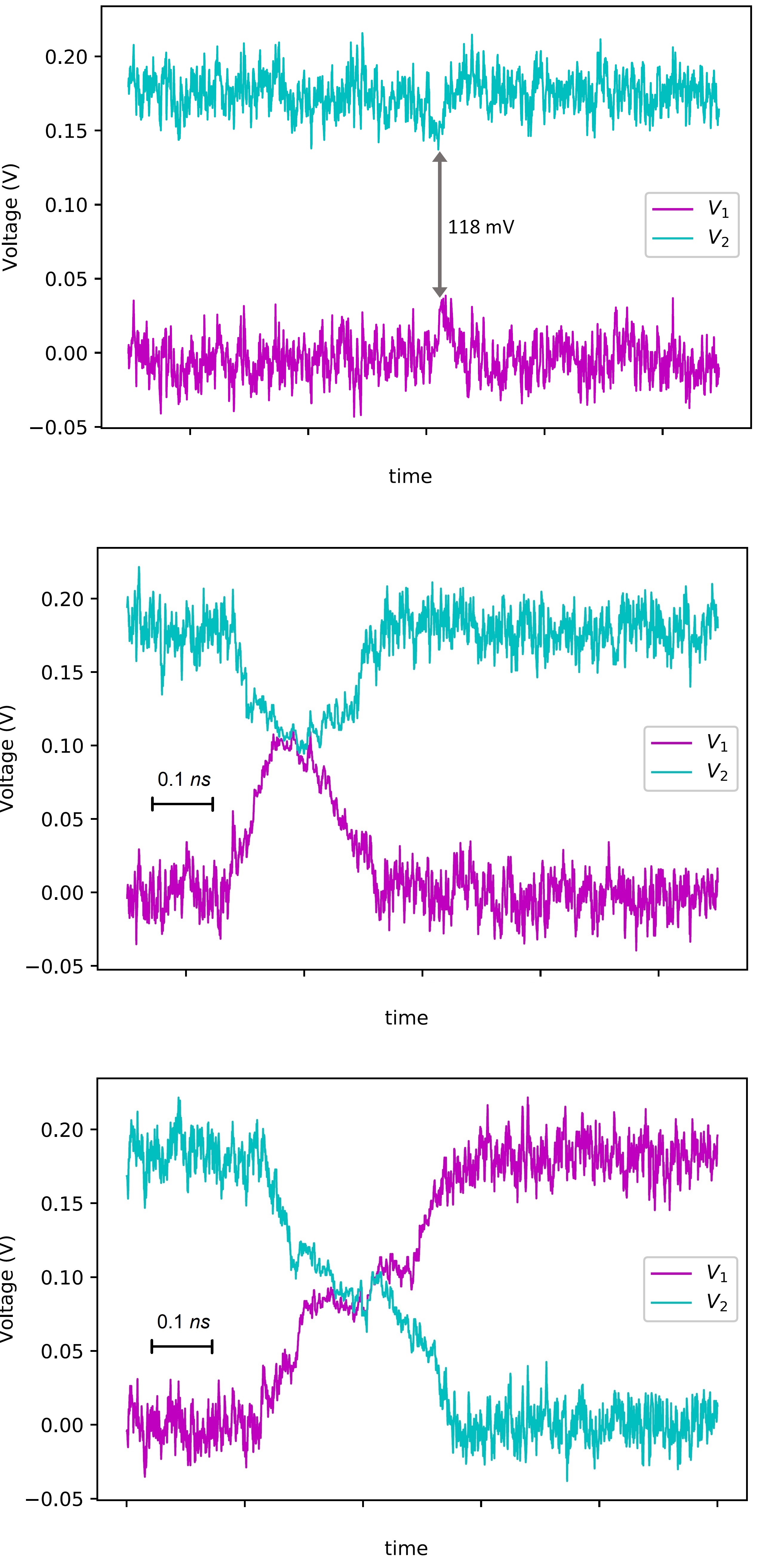

Finally, we have extended our approach to analyze the reliability of latches and SRAMs operating in subthreshold conditions. We were able to evaluate how reliability due to thermal noise of SRAMs built from 7nm finFET technology were affected by lowered supply voltage, increased process variability, and temperature shifts. Our work has made it possible to quantitatively evaluate in minutes the asymptotic behavior of extremely rare error events that lead to bit-flip errors. Again, such an analysis would be impossible with conventional SPICE-based transient simulation methods. Another nice feature of our work is that our simulation framework can be adapted to other technology nodes or other sources of noise, and provides a means of evaluating the trade-offs in the robust design of low-power SRAM for ultra-low-power memory.

Here are some of my publications related to the topic.

- . A Fast Simulator for the Analysis of Sub-Threshold Thermal Noise Transients. DAC 2016. PDF

- A Subthreshold Noise Transient Simulator Based on Integrated Random Telegraph and Thermal Noise Modeling. IEEE TCAD 2018. PDF

- Thermal Noise-Induced Error Simulation Framework for Subthreshold CMOS SRAM. S3S 2019. PDF

- Fundamental Thermal Limits on Data Retention in Low-Voltage CMOS Latches and SRAM. IEEE TDMR 2020. PDF