### Reliable Computing at the Nanoscale

by Eric Rachlin ScB, Brown University, 2003 ScM, Brown University, 2006

A Dissertation submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in the Department of Computer Science at Brown University

This dissertation by Eric Rachlin is accepted in its present form by the Department of Computer Science as satisfying the dissertation requirement for the degree of Doctor of Philosophy.

| Date | John E. Savage, Director                  |

|------|-------------------------------------------|

|      | Recommended to the Graduate Council       |

| Date | John E. Savage, Reader                    |

| Date | André DeHon, Reader                       |

| Date | Franco P. Preparata, Reader               |

|      | Approved by the Graduate Council          |

| Date | Sheila Bonde, Dean of the Graduate School |

### Vitæ

After graduating from Stuyvesant High School in New York City, Eric Rachlin began his multidecade stint at Brown University. In 2003, Eric graduated magna cum laude with an Sc.B. in Applied Math and Computer Science. In the summer of 2003, he began working as a research assistant to Computer Science Professor John Savage. Collaborating closely with Professor Savage, he investigated the resource requirements of stochastically assembled nanowire-based memories. He also helped draft a successful NSF NIRT proposal that would later fund the bulk of his PhD research.

In the fall of 2004, Eric reenrolled at Brown to pursue his Ph.D. in nanoscale computing. As a graduate student, Eric's primary research interests included probabilistic analysis, stochastic nanoscale assembly, information theory and reliable computation. Eric's research has focused on demonstrating how emerging nanoscale architectures can be modeled probabilistically and made robust against random variations. He has analyzed a range of proposed nanoscale devices, and has also explored how error-correcting codes can be employed to perform reliable nanoscale computations.

In addition to his work on nanoscale computing, Eric has collaborated with researchers in computer vision, P2P networks and cryptography. He has also helped teach several courses on computational complexity. Outside of the world of computer science research, Eric is involved with the design and maintenance of several high-traffic blogs, including passive aggressive notes.com, winner of a 2008 SXSWi WebAward. He is also an extremely proficient juggler and avid drummer.

Dedicated to my grandfather for investing in my Brown education

## Acknowledgements

First and foremost I would like to thank John Savage. During my time at Brown, John has not only been an advisor and collaborator, but also a friend and mentor. His continual advice and support with regard to research, my career, and life in general, will serve me for years to come. I must also thank our primary collaborators, André DeHon, Ben Gojman and Charles Lieber. André, in particular, brought crucial expertise to John and my research. This thesis would not have been possible without his contribution on several publications, as well as on the grants that funded my graduate career. His service on my thesis committee is also greatly appreciated. Similarly, I thank Franco Preparata for serving on both my research comps and thesis committees, and for taking an ongoing interest in my work.

In addition to my other collaborators, Mira Belenkiy, Melissa Chase, Chris Erway, John Jannotti, Alp Kupcu, Anna Lysyanskaya and Yue Wu, I would also like to thank the many friends who made my time at Brown more than just a research endeavor. In particular, Chris Erway and Tibet Sprague continually got me out of the house and reminded me of the importance of life beyond the CS department (while simultaneously showing me a thing or two about how to write code). Harry Siple, David Segal and Daniel Bass not only made living in Providence significantly more enjoyable, but conveniently provided me with a place to stay during my many trips back to town while living in New York City.

Finally, I would like to thank my family, especially my parents for their perpetual support and encouragement, my grandmothers for their remarkable interest in any and all Eric-related activities (despite having never used a computer), and my grandfather for his substantial contribution to my early years at Brown. Most importantly, I would like to thank the lovely and talented Jessica Purmort for her continual reminder that, more than anything, I needed to hurry up and finish this thing already!

# Contents

| D        | edica | tion   |                                                  | $\mathbf{v}$ |

|----------|-------|--------|--------------------------------------------------|--------------|

| 1        | Intr  | oducti | ion                                              | 1            |

|          | 1.1   | Reliab | ble Nanoscale Computation                        | 2            |

|          |       | 1.1.1  | A Brief History of Nanocomputing                 | 2            |

|          |       | 1.1.2  | Device Reliability and General Purpose Computing | 7            |

|          | 1.2   | Funda  | amental Characteristics of Nanoscale Computing   | 9            |

|          |       | 1.2.1  | Stochastic Assembly                              | 9            |

|          |       | 1.2.2  | Post-Assembly Testing and Configuration          | 10           |

|          |       | 1.2.3  | Strict Assembly Constraints                      | 10           |

|          |       | 1.2.4  | Imperfect Operation                              | 10           |

|          | 1.3   | An Ov  | verview of this Thesis                           | 11           |

| <b>2</b> | Ove   | erview | of Nanoscale Computing                           | 12           |

|          | 2.1   |        | ology Overview                                   | 12           |

|          |       | 2.1.1  | Nanoscale Semiconductor-Based Architectures      | 12           |

|          |       | 2.1.2  | DNA-Based Assemblage                             | 13           |

|          |       | 2.1.3  | Quantum-Dot Cellular Automata                    | 14           |

|          |       | 2.1.4  | Biological Computing                             | 15           |

|          | 2.2   | Nanov  | vire Crossbars                                   | 15           |

|          |       | 2.2.1  | Crossbar Assembly                                | 16           |

|          |       | 2.2.2  | Crossbar-based Memories                          | 17           |

|          |       | 2.2.3  | Crossbar-based Logic                             | 19           |

| 3        | Nar   | nowire | Decoders                                         | 22           |

|          | 3.1   | Decod  | ler Requirements                                 | 22           |

|          |       | 3.1.1  | Nanowire Addressing                              | 22           |

|          |       | 3.1.2  | Address Requirements                             | 24           |

|          |       | 3.1.3  | Simple Versus Compound Decoders                  | 24           |

|          | 3.2   | Decod  | ling Technologies                                | 25           |

|          |       | 3.2.1  | Encoded Nanowire Decoders                        |              |

|          |       | 3.2.2  | Mask-Based Decoders                              |              |

|          |       | 3 2 3  | The Randomized-Contact Decoder                   | 28           |

|   |     | 3.2.4 Additional Decoding Technologies                   | <br>29 |

|---|-----|----------------------------------------------------------|--------|

|   | 3.3 | Post-Assembly Configuration                              | <br>31 |

|   |     | 3.3.1 Address Discovery                                  | <br>31 |

|   |     | 3.3.2 Address Translation Circuitry                      | <br>32 |

|   | 3.4 | Modeling Nanowire Decoders                               | <br>33 |

|   |     | 3.4.1 The Binary Model of Nanowire Control with Errors   | <br>33 |

|   |     | 3.4.2 Real-valued Physical Models                        | <br>36 |

|   | 3.5 | Decoder Analysis Framework                               | <br>38 |

|   |     | 3.5.1 Memory Area Estimate                               | <br>39 |

|   |     | 3.5.2 Memory Addressing Strategies                       | <br>39 |

|   |     | 3.5.3 Expectation versus with High Probability           | <br>41 |

| 4 | The | Randomized-Contact Decoder                               | 42     |

|   | 4.1 | Bounds Using Inclusion-Exclusion                         | <br>42 |

|   |     | 4.1.1 A Single Contact Group                             | <br>43 |

|   |     | 4.1.2 Multiple Contact Groups                            | <br>46 |

|   | 4.2 | Bounds Using Expectation                                 | <br>47 |

|   |     | 4.2.1 A Single Contact Group                             | <br>47 |

|   |     | 4.2.2 Multiple Contact Groups                            | <br>48 |

|   |     | 4.2.3 Additional Addressing Strategies Using Expectation | <br>50 |

|   | 4.3 | Comparison of Addressing Strategies                      | <br>50 |

|   | 4.4 | Summary of Results                                       | <br>51 |

| 5 | Enc | oded Nanowire Decoders                                   | 53     |

|   | 5.1 | NW Encodings                                             | <br>54 |

|   |     | 5.1.1 Code Requirements                                  | <br>55 |

|   |     | 5.1.2 $(h, M)$ -Hot Codes                                | <br>56 |

|   |     | 5.1.3 Binary Reflected Code                              | <br>57 |

|   |     | 5.1.4 Generating Random Ensembles of Axial Codewords     | <br>57 |

|   | 5.2 | Analysis of Encoded NW Decoders                          | <br>58 |

|   |     | 5.2.1 Bounds Using Expectation                           | <br>58 |

|   |     | 5.2.2 Bounds Using Inclusion-Exclusion                   | <br>62 |

|   |     | 5.2.3 Area Estimates                                     | <br>64 |

|   | 5.3 | Misalignment of Axial Codes                              | <br>66 |

|   | 5.4 | Radially Encoded Nanowire Decoders                       | <br>67 |

|   |     | 5.4.1 The Linear Radially Encoded NW Decoder             | <br>67 |

|   |     | 5.4.2 The Linear-Logarithmic Radially Encoded NW Decoder | <br>69 |

|   |     | 5.4.3 The Fully Logarithmic Radially Encoded NW Decoder  | 70     |

|   |     | 5.4.4 Fault-tolerant Etching Error Correction            |        |

|   |     | 5.4.5 Hybrid Nanowire Codes and Decoders                 |        |

|   | 5.5 | Summary of Results                                       | 7/     |

| 6 | Mas | sked-Based Decoders 75                                  |

|---|-----|---------------------------------------------------------|

|   | 6.1 | Modeling Decoder Manufacture                            |

|   |     | 6.1.1 LR Manufacture                                    |

|   |     | 6.1.2 Modeling Variation in Mask Placement              |

|   |     | 6.1.3 Modeling Variation in LR Boundary Placement       |

|   |     | 6.1.4 InterNW Regions                                   |

|   |     | 6.1.5 Additional Sources of LR Boundary Variation       |

|   | 6.2 | Analyzing the <i>n</i> -Cycle Mask-Based Decoder        |

|   |     | 6.2.1 Models for Decoder Analysis                       |

|   | 6.3 | Coupon Collection                                       |

|   |     | 6.3.1 The Coupon Collector Problem with Failures        |

|   |     | 6.3.2 The Targeted Coupon Collector Problem             |

|   |     | 6.3.3 The Multi-Stage Targeted Coupon Collector Problem |

|   | 6.4 | Performance of the <i>n</i> -Cycle Mask-Based Decoder   |

|   |     | 6.4.1 The Coarse-Grained Model                          |

|   |     | 6.4.2 The Fine-Grained Model                            |

|   | 6.5 | Additional Considerations                               |

|   |     | 6.5.1 Address Translation Circuitry                     |

|   |     | 6.5.2 Alternative Addressing Strategies                 |

|   | 6.6 | Summary of Decoder Analysis                             |

| 7 | Nar | nowire Addressing for Crossbar-based Logic 95           |

|   | 7.1 | NW Decoders for Logic                                   |

|   | 7.2 | Stochastic Assembly of NW Logic Decoders                |

|   |     | 7.2.1 Unique Couplings                                  |

|   |     | 7.2.2 Area Bounds                                       |

|   | 7.3 | Lower Bounding $\beta$                                  |

|   |     | 7.3.1 A Lower Bound for RCDs                            |

|   |     | 7.3.2 A Lower Bound for Encoded NW Decoders             |

|   | 7.4 | Stochastic Crossbar Interconnect                        |

| _ | •   |                                                         |

| 8 |     | nowire Address Discovery 106                            |

|   | 8.1 | Address Discovery via Read/Write Operations             |

|   |     | 8.1.1 Coping with Errors                                |

|   | 8.2 | Exhaustive Search                                       |

|   |     | 8.2.1 Parallel Exhaustive Search                        |

|   |     | 8.2.2 Coping With Codeword Errors                       |

|   | 8.3 | Encoded NW decoders                                     |

|   |     | 8.3.1 Binary Search                                     |

|   |     | 8.3.2 Searching Across Contact Groups                   |

|   |     | 8.3.3 A Lower Bound                                     |

|   |     | 8.3.4 Coping With Misalignment Errors                   |

|   | 8.4 | Arbitr | ary Codes                                             |

|---|-----|--------|-------------------------------------------------------|

|   |     | 8.4.1  | Asymptotic analysis                                   |

|   |     | 8.4.2  | Experimental Results                                  |

| 9 | Cod | led Co | mputation 118                                         |

|   | 9.1 | Appro  | aches to Reliable Computation                         |

|   |     | 9.1.1  | Modular Redundancy                                    |

|   |     | 9.1.2  | Two-Tiered Reliability and Coded Computation          |

|   |     | 9.1.3  | Previous Work on Coded Computation                    |

|   | 9.2 | A Moo  | del of Computation                                    |

|   |     | 9.2.1  | Formalizing the Model                                 |

|   |     | 9.2.2  | Examples                                              |

|   | 9.3 | The C  | oded Computation Framework                            |

|   |     | 9.3.1  | One Step of Coded Computation                         |

|   |     | 9.3.2  | Transcoding the Output                                |

|   |     | 9.3.3  | Conditions on Permutations                            |

|   |     | 9.3.4  | Spielman's Model                                      |

|   | 9.4 | Interp | olation Polynomials                                   |

|   |     | 9.4.1  | Examples of interpolation polynomials                 |

|   |     | 9.4.2  | Applying Polynomials to Linear Codes                  |

|   | 9.5 | Transo | coding                                                |

|   |     | 9.5.1  | Transcoding Using 2D Codes                            |

|   |     | 9.5.2  | Transcoding Using Checksums                           |

|   |     | 9.5.3  | Transcoding in Parallel Architectures                 |

|   | 9.6 | Codew  | vord Permutations                                     |

|   |     | 9.6.1  | Direct Application of Extension Permutations          |

|   |     | 9.6.2  | Composing Permutations to Realize Extensions of $\Pi$ |

|   |     | 9.6.3  | Data-Movement Overhead                                |

|   | 9.7 | Famili | es of Codes                                           |

|   |     | 9.7.1  | Reed-Solomon Codes                                    |

|   |     | 9.7.2  | Reed-Muller Codes                                     |

|   |     | 9.7.3  | Other Polynomial Codes                                |

|   |     | 9.7.4  | Multidimensional Codes                                |

|   | 9.8 | Overh  | ead                                                   |

|   |     | 9.8.1  | Reliability via Repetition                            |

|   |     | 9.8.2  | Basic Analysis Framework                              |

|   |     | 9.8.3  | Coded Computation Using 2D Codes                      |

|   |     | 9.8.4  | Coded Computation Using 1D Codes                      |

|   |     | 9.8.5  | Summary of Results                                    |

| 10 E | xp  | loring  | the Power of Coded Computation         |  | 15   | 5 |

|------|-----|---------|----------------------------------------|--|------|---|

| 10   | ).1 | Lower   | Bounds                                 |  | . 15 | 5 |

| 10   | 0.2 | Efficie | ently Encoding Most-Boolean Function   |  | . 15 | 8 |

|      |     | 10.2.1  | Pippenger's Construction               |  | . 15 | 9 |

| 10   | 0.3 | Coded   | l Prefix Computations                  |  | . 16 | 0 |

|      |     | 10.3.1  | Encoding a Parallel Prefix Computation |  | . 16 | 1 |

|      |     |         |                                        |  |      |   |

| 11 C | on  | clusio  | n                                      |  | 16   | 3 |

# List of Tables

| 10.1 | Α | 3-step | parallel | prefix | computation | on a | hypercube |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 16 | 3] |

|------|---|--------|----------|--------|-------------|------|-----------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|----|

|------|---|--------|----------|--------|-------------|------|-----------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|----|

# List of Figures

| 1.1 | Richard Feynman                                                       | 2  |

|-----|-----------------------------------------------------------------------|----|

| 1.2 | Early Integrated Circuits                                             | 3  |

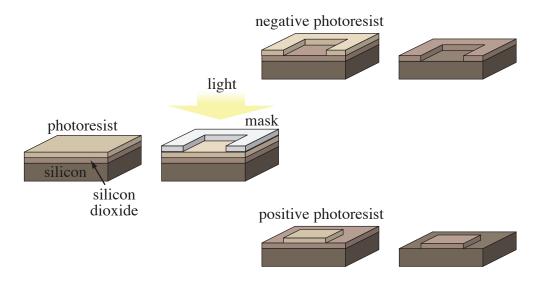

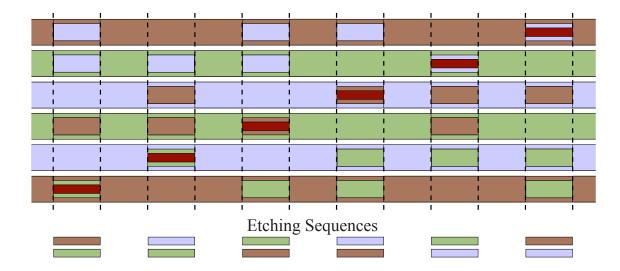

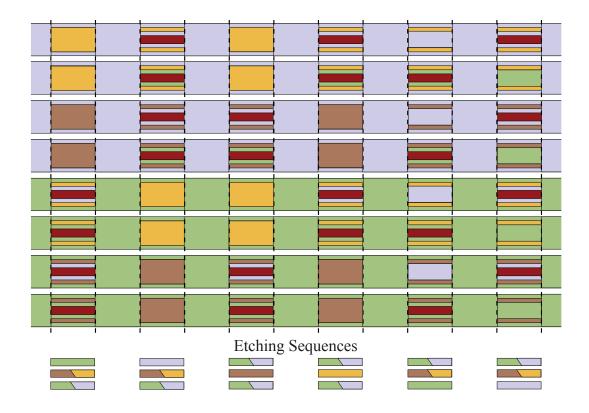

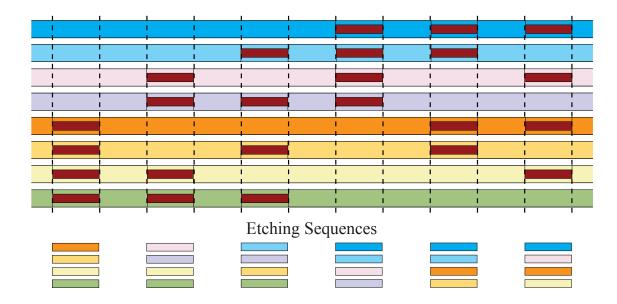

| 1.3 | The etching of a chip via photolithography                            | 4  |

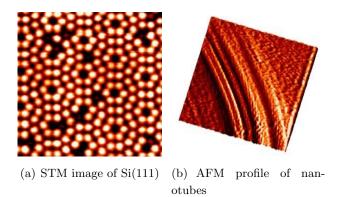

| 1.4 | Atomic scale microscopy from an STM and AFM                           | 5  |

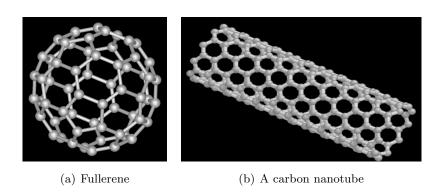

| 1.5 | Wireframe models of fullerene and a carbon nanotube                   | 5  |

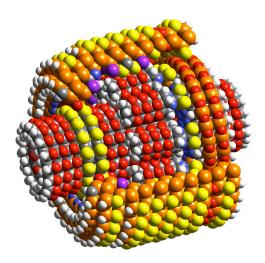

| 1.6 | A theoretical molecular machine                                       | 6  |

| 2.1 | A range of semiconductor-based nanoscale computing technologies       | 13 |

| 2.2 | Stochastically assembled DNA structures                               | 14 |

| 2.3 | Circuits based on quantum-dot cellular automata                       | 15 |

| 2.4 | A programmable nanowire crossbar                                      | 16 |

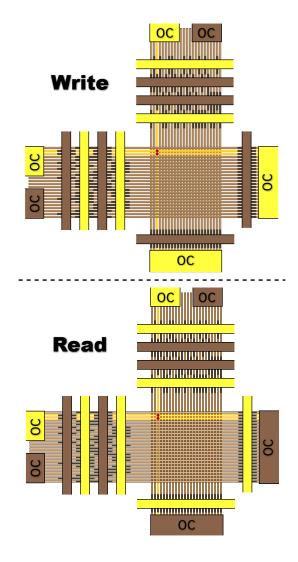

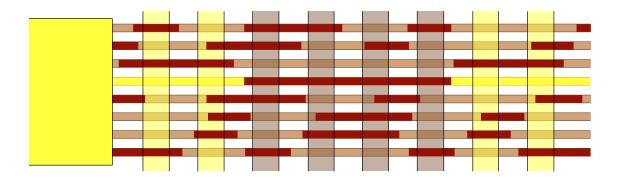

| 2.5 | A nanowire crossbar-based memory performing read and write operations | 18 |

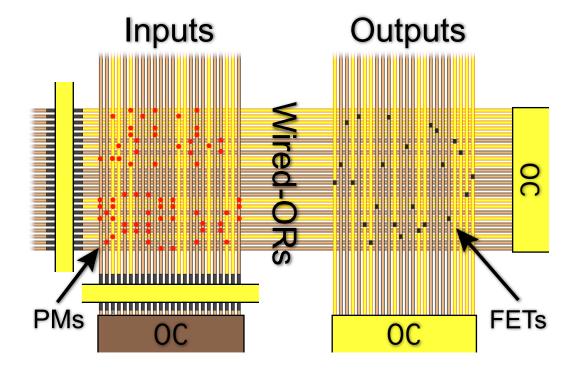

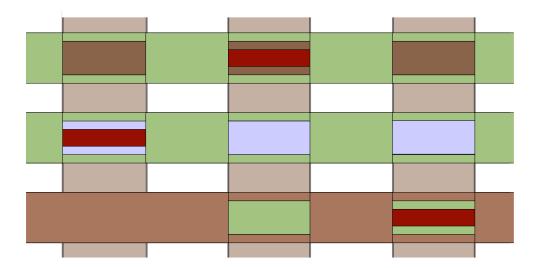

| 2.6 | A level of reconfigurable crossbar-based logic                        | 20 |

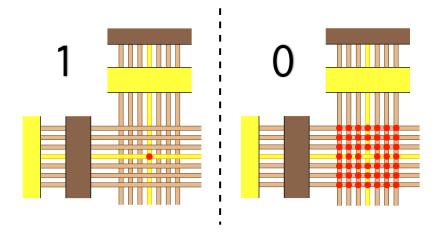

| 3.1 | The two extreme cases when reading data from a nanowire crosspoint    | 23 |

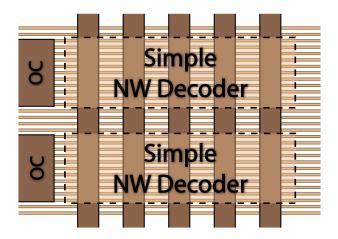

| 3.2 | A compound nanowire decoder                                           | 25 |

| 3.3 | An axially encoded nanowire decoder                                   | 26 |

| 3.4 | A radially encoded nanowire decoder                                   | 27 |

| 3.5 | A masked-based nanowire decoder                                       | 28 |

| 3.6 | A randomized-contact nanowire decoder                                 | 29 |

| 3.7 | Rotational offset decoders                                            |    |

| 3.8 | MNAB                                                                  | 31 |

| 3.9 | Address translation circuity used to interface a nanowire decoder     | 32 |

| 4.1 | Codewords in a randomized contact nanowire decoder                    | 43 |

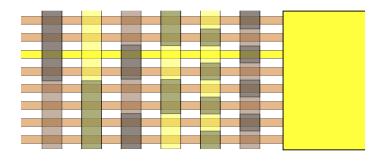

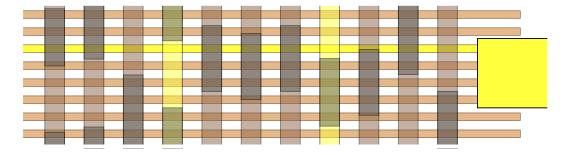

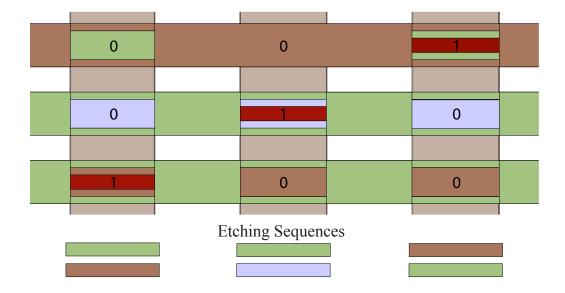

| 5.1 | Axially encoded nanowire codewords                                    | 54 |

| 5.2 | Radially encoded nanowire codewords                                   | 55 |

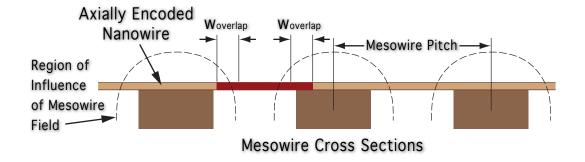

| 5.3 | Schema for calculating the probability of axial misalignment          | 66 |

| 5.4 | A linear radially encoded nanowire decoder                            | 68 |

| 5.5 | A linear radially encoded nanowire decoder                            | 71 |

| 5.6 | A logarithmic radially encoded nanowire decoder                       | 72 |

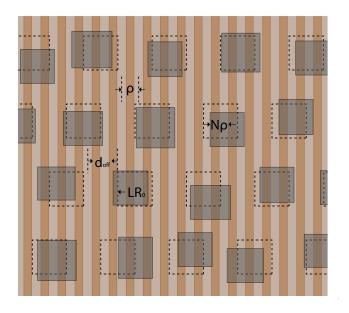

| 6.1 | A masked-based nanowire decoder                                       | 76 |

| 6.2 | A cycle of high-K dielectric lithographic regions                     | 78 |

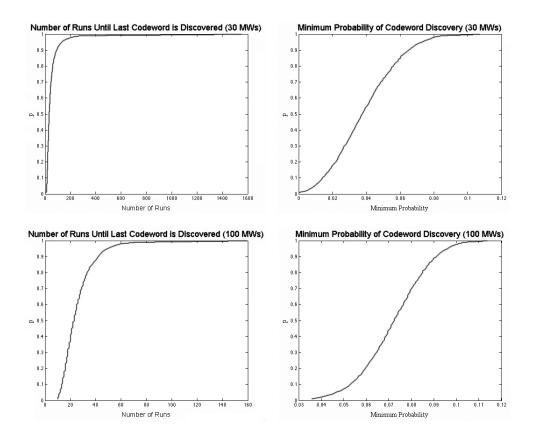

| 8.1 | Codeword Discovery via Randomized Testing | 117 |

|-----|-------------------------------------------|-----|

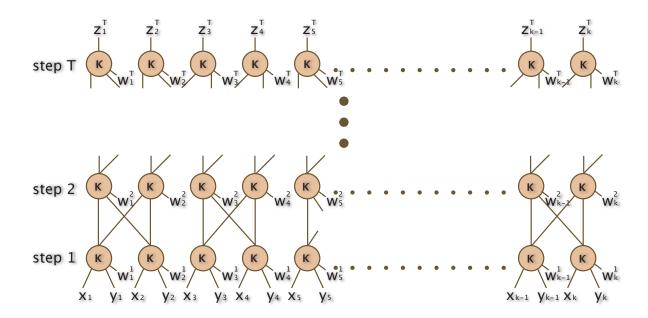

| 9.1 | A T-step regular computing network        | 122 |

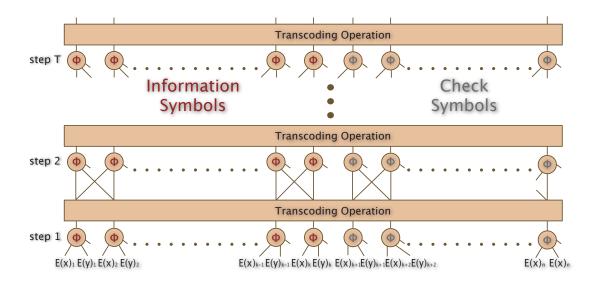

| 9.2 | A T-step coded computation                | 128 |

### Chapter 1

### Introduction

Emerging nanoscale computing technologies necessitate fundamental changes in the way computer architectures are designed and analyzed. The significant uncertainty associated with the assembly and operation of nanoscale devices must not only be modeled and accounted for, but actively embraced as part of the design process. In stark contrast with today's VLSI, probabilistic modeling and analysis are primary requirements for the successful realization of nanoscale computer architectures.

In this thesis we examine how faults, defects and unavoidable nanoscale variation can be tolerated in emerging nanoscale computer architectures. The first portion of this thesis focuses on the nanowire crossbar, a particularly promising building block for near-term nanoscale hardware. In the context of the crossbar, we describe how a range of stochastic nanoscale fabrication technologies can be used to reliably address (i.e. control) nanoscale wires. We provide tight analytic bounds on the resources required to cope with stochastic nanoscale assembly. We also demonstrate a range of promising design strategies.

A technical overview of the nanowire crossbar and related nanowire addressing technologies is provided in Chapters 2 and 3. The chapters provide the background and models utilized in the analysis of Chapters 4 through 8. These chapters collectively explore a number of related approaches for integrating stochastically assembled crossbar-based nanoscale hardware with traditional lithographically produced mesoscale hardware. More importantly, they explicitly demonstrate the type of probabilistic modeling and analysis that is vital to the success of nanoscale computing.

The second portion of this thesis investigates the more general problem of performing reliable computations using unreliable devices. Designing architectures that function properly in the presence of transient faults (for example, building circuits out of gates that occasionally produce incorrect outputs) has been a longstanding challenge in the fields of computer science and computer engineering. In the context of nanoscale technologies the problem is particularly pressing, as it is anticipated that nanoscale devices will be significantly less reliable than their current mesoscale counterparts.

To attack this problem, Chapter 9 demonstrates the promise of "two-tiered" reliability, meaning the structuring of computations such that some operations are much more reliable than others. Two-tiered reliability reflects the ability of highly reliable mesoscale devices to supervise less reliable nanoscale devices. As such, it represents an important design paradigm that is likely to become

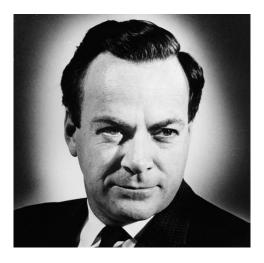

Figure 1.1: The potential for nanoscale computing was first described by Richard Feynman in his 1959 speech to the American Physical Society. In recognition of his early vision of where computers were headed, the Foresight Nanotech Institute awards an annual Feynman Prize for significant advancements in nanotechnology.

increasingly prominent as computer architectures continue to shrink. What's more, the utility of circuits and algorithms that employ tiered reliability is not limited to nanoscale architectures. For example, up-and-coming multicore chips may contain cores that operate at varying levels of reliability (since highly reliable cores likely require more area, power or time per operation). Such cores could be used to implement algorithms that have been designed with tiered reliability in mind.

### 1.1 Reliable Nanoscale Computation

This section presents the broader context for the research on reliable nanoscale computation contained in this thesis. It begins with a brief history of nanoscale computing. This is followed by a discussion of the historic importance of device reliability in digital hardware. Both sections highlight the significant challenges currently facing the design and implementation of reliable nanoscale architectures.

### 1.1.1 A Brief History of Nanocomputing

One nanometer, or  $10^{-9}$  meters, is the length of a single sugar molecule, and a cubic nanometer provides only enough room for a few hundred carbon atoms. It may never be possible to create novel arrangements of subatomic particles, and as such, a nanometer represents the approximate lower limit on the size of technology. While nanometer-scale technology, or "nanotechnology", has a wealth of applications, nanoscale computing is among the most prominent. What's more, the successful realization of reliable nanoscale computation would serve as a crucial step towards the realization of other nanotechnologies that require the integration of a large number of functional nanoscale devices.

(b) An early integrated circuit produced using photolithography

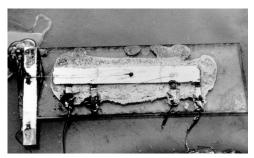

Figure 1.2: In the late 1950s, two companies independently developed semiconductor-based integrated circuits. In 1958, Jack Kilby developed the first integrated circuit (a) at Texas Instruments as a summer research project. In 1959 Fairchild Semiconductor patented a process for producing planar semiconductor devices. Soon after, Robert Noyce demonstrated that this process could be adapted to produce general purpose integrated circuits within silicon chips (b). In 1968, Noyce went on to cofound Intel with his colleague Gordon Moore.

The dream of nanoscale computing was first articulated by Richard Feynman (see Figure 1.1) in his 1959 speech given to the American Physical Society. He argued that no known physical law would prevent the room-sized computers of the 1950s from being replaced with far more powerful, pin-sized computers built from nanoscale components. As many at the time realized, general purpose computers were poised to become vastly more useful once their computing power increased by several orders of magnitude. This has long since come to pass, but we are only now approaching the nanoscale devices that Feynman asserted we could one day produce.

At the time of Feynman's speech, computer hardware was undergoing a major transition. The bulky vacuum tube-based logic of the 1950s was being replaced with solid-state transistors (see Figure 1.2). Crucially, solid-state transistors can be manufactured using light-based etching, known as photolithography. This allows for the efficient production of microscopic circuits compactly embedded into the surface of a silicon chip. Modern computer chips, which are often referred to as VLSI (very large scale integration) technology, are manufactured using photolithography.

Since the 1960s, photolithography has allowed for ever-smaller, ever-faster VLSI processors comprised of semiconductor-based logic that operates at high speeds and high levels of reliability. What's more, it allows for millions of identical copies of a computer chip to be produced from a single set of masks. These masks act like blueprints for a top-down assembly process. By shining light through the masks, complex two-dimensional patterns can be repeatedly etched into successive layers of a silicon wafers (see Figure 1.3). Selective application of dopants to different portions of the pattern produces functional devices, like logic gates. Metallic wires, which connect these devices, can also be produced by depositing a conductor into etched regions.

Starting in the 1960s, it became apparent that photolithographically produced computer hardware obeyed an empirical trend. With remarkable consistency, the area required for digital logic

Figure 1.3: In photolithography, light is shown through a mask to define which regions of either positive or negative photoresist are removed. The remaining resist is then used to etch patterns into layers of a silicon and silicon dioxide. Functional devices can then be created by selectively depositing dopant, conductors, and other materials into the etched away regions. By repeating this entire process, multilayer chip-based architectures are built up one level at a time.

was cut in half approximately every 18 months. This in turn meant that the number of transistors on a chip, and hence the number of computations it could perform, approximately doubled every 18 months. This general trend, which is typically referred to as "Moore's Law", has become increasingly difficult and costly to maintain. The feature size of today's chips, meaning the minimum spacing between wires and gates, is 45 nanometers (nm). While computer manufactures would like nothing more than to shrink features further, doing so necessarily means confronting the challenges of nanoscale manufacturing.

Feynman's prescient, but highly speculative vision of nanoscale engineering gained significant focus in the 1980s. The advent of the scanning tunneling microscope (STM), and later the atomic force microscope (AFM) led to an increasingly precise understanding of how atoms are configured within molecules. An STM scans across the surface of a material with an atomic-scale tip. Electron tunneling between the tip and the surface produces a current. By measuring this current (or alternatively, adjusting the height of tip to maintain a constant current) STMs are able to obtain sub-nanometer resolution images of a sufficiently clean surface (see Figure 1.4a). Prior to the STM electron-based microscopy (which has existed since the 1930s) had great difficulty imaging molecular-scale structures. Soon after the STM, AFMs provided scientists with additional molecular-scale imaging capabilities. By precisely measuring the deflection an atomic-scale tip, AFMs are able to reveal the three-dimensional profile of a surface at the atomic scale (see Figure 1.4b).

An improved understanding of molecular structures facilitated, among other things, the discovery of fullerene, or "buckyballs", in 1985 and carbon nanotubes in 1992. Both are large carbon

Figure 1.4: Starting in the 1980s, scientists gained the ability to directly observe the structure of molecules. In a) a scanning tunneling microscope (STM) reveals the structure of a 5.4nm x 5.4nm segment of silicon crystal. In b) an atomic force microscope (AFM) provides the three-dimensional profile of single-walled carbon nanotubes within a 15.8 nm x 15.8 nm patch. Both images were obtained via Omicron Nanotechonlogy GmbH and are available on their website at http://omicron.de/index2.html?/results/~Omicron.

Figure 1.5: Both fullerene molecules and carbon nanotubes are comprised of carbon atoms arranged in a highly regular geometric structure. Fullerene's, for example, are so named because their structure is identical to that of a geodesic dome, a building design first patented and popularized by Buckminster Fuller.

Figure 1.6: A differential gear of the type put forth in Drexler's 1992 book, Nanosystems: Molecular Machinery, Manufacturing and Computation. Here a molecular shaft, surrounded by "bearings", would be able to rotate independently of the molecular casing. This image was produced by Institute for Molecular Manufacturing and is available a http://www.imm.org/research/parts/gear/ (Copyright 1997 IMM, all rights reserved).

molecules in which individual carbon atoms serve as the building blocks of highly regular geometric structures (see Figure 1.5). These structures, which closely resemble manmade geodesic domes, sparked a renewed enthusiasm for nanoscale engineering. Suddenly it appeared feasible for macroscale designs to be recreated as nanoscale structures.

The capabilities of the AFM furthered this excitement, as its molecular tip could be used not just to image surfaces, but to nudge and manipulate individual molecules. This suggested to some the possibility of building, atom-by-atom, molecular scale machines that could in turn facilitate the production of additional molecular scale components. An early and highly prominent advocate of this research agenda was Eric Drexler. In his 1986 book, Engines of Creation: The Coming Era of Nanotechnology [1], Drexler suggested that general purpose molecular scale assemblers could one day be constructed and used to bootstrap a wide array of modular nanoscale devices.

Nanosystems: Molecular Machinery, Manufacturing and Computation [2], Drexler's 1992 book based on his PhD Thesis, further popularized his vision of nanoscale structures that act like thermodynamically powered, substantially scaled-down versions of traditional macroscale machinery (see Figure 1.6). Drexler's writings also sparked concern that nanoscale machinery had the potential to one day run amok as unstoppable, self-replicating "grey goo". Some scientists, however, became highly critical of Drexler's view. Nanoscale engineering, they argued, could only be expected to produce structures that are compatible with highly stochastic assembly process. As a result, nanotechonlogy could not simply be envisioned as miniscule recreations of traditional technology.

Chemist and Nobel Laureate Richard Smalley, was among the most vocal of Drexler's critics. In 2001, he asserted that the so-called "fat fingers" and "sticky fingers" of even microscale manufacturing technology pose a huge challenge when trying to deterministically arrange the atomic

building blocks of hypothetical nanoscale machinery [3]. In other words, randomness is inherent to molecular assembly, and theoretical nanoscale designs that rely on arbitrary arrangements of hundreds of molecules may well be impossible to realize in practice. As such, nanotechnology must be designed and assembled in ways that are fundamentally different from how current technology is engineered. Probabilistic analysis is crucial.

Smalley's perspective is much more in line with the current state of nanotechnology research. In the past decade, billions of dollars has gone into funding the work of chemists, physicist and engineers. Although many novel nanoscale structures have been discovered and analyzed, techniques for general purpose molecular assembly remain elusive. Instead, slow and steady progress has resulted from the careful refinement of more traditional chemical processes. Even if molecular assemblers are an eventual possibility, they are unlikely to play a role in the manufacturing of near-term nanoscale computer architectures.

Since the year 2000, a number of individual nanoscale computing devices (e.g. wires, logic gates and memory cells) have been demonstrated. Producing architectures from these devices, however, is not simply a matter of substituting tiny wires and gates into today's architectures. Designers of nanoscale architectures must find ways to interconnect millions, or billions of devices, even while our ability to place individual devices remains poor. Furthermore, as we continue to push the limits of what can be reliably manufactured, we must find new ways to mitigate device variation. If nanoscale architectures are to be realized any time soon, they will have to function correctly even when individual devices fail. Although no nanoscale architectures have yet been produced, most researchers believe that they will incorporate stochastic assembly, reconfigurability, fault-tolerance and strict design constraints [4, 5].

Below, Section 1.2 elaborates on these four requirements. As explained in the first half of Chapter 2, they are relevant to a range of proposed nanoscale computing technologies. Nonetheless, much of the analysis in this thesis focuses on today's most viable nanotechnology, the nanowire crossbar. Nanowire crossbars provide a relatively concrete model of what nanoscale computing may look like (see Section 2.2), while at the same time highlighting many of the more general issues facing alternative nanoscale computing technologies. To date, the crossbar is the only nanoscale architectural component to have been demonstrated [6, 7, 8]. Furthermore, a number of crossbar-based designs have been proposed, demonstrating how crossbars can serve as a basis for both memories and circuits [9, 10, 11, 12, 13] (see Section 2.2).

#### 1.1.2 Device Reliability and General Purpose Computing

Many of the fundamental ideas behind general purpose digital computing can be traced back not just to Alan Turing in 1930s, but to Charles Babbage in the 19th century. Despite his insights, however, Babbage was unable to construct his "Analytical Engine" using the fabrication technology of his time. Without reliable components, general purpose computing machines proved prohibitively difficult to implement. Instead, the successful realization of digital computers would have to wait until 1940s, when electronic components with high on/off ratios permitted the reliable implementation of digital logic.

Since then, the overwhelming success of general purpose computing has been continually fueled

by a stream of steadily shrinking, highly reliable hardware. Today, increasingly complex architectures are designed using ever-smaller, ever-faster processors comprised of logic gates that operate at astronomically high levels of reliability. Assume, for example, a hypothetical representative architecture consisting of 1,024 3GHz processors with 10<sup>9</sup> gates/processor. During a full year of operation, this collection of processors might perform as many as 10<sup>29</sup> gate operations.

Now suppose that any given output of any given gate has probability  $p_f$  of being incorrect. If we assume that neither the processors, nor the programs run on them, are designed to accommodate errors, a 99% chance of fault free operations potentially requires that  $p_f < 10^{-31}$ ! Even if we acknowledge that, at any given time, some fraction of the gates do not effect the output of the computation, our required value of  $p_f$  remains staggeringly minute.

As the size of individual gates shrinks and the number of gates per chip increases, it becomes increasingly burdensome to maintain such an astronomically high level of gate reliability. Up-and-coming nanoscale devices and multicore architectures both point to an impending need for fault-tolerant circuits and software. The ability to tolerate gate level faults would not only pave the way for larger architectures with smaller features sizes, it could allow current CMOS-based chips to operate at higher speeds or lower power. ("CMOS", or complementary metaloxidesemiconductor, refers to the design and manufacturing techniques used to implement the digital logic on today's chips.)

Early digital computers were built using vacuum tubes, which were unreliable. This presented the same type of scaling challenge we face today. As computers became increasingly complex (i.e. used more logic gates), the probability that some component would fail during a given computation approached 1. This motivated von Neumann, in his well-known 1956 paper [14], to propose a systematic approach to building logic from unreliable gates. He described how an arbitrary circuit, C, built from perfectly reliable gates, could be converted to a fault-tolerant circuit C', constructed from potentially faulty gates. This construction involved repeating each gate r times, and then suppressing errors with constant-sized, but potentially faulty, majority gates (see Chapter 9).

Although von Neumann's work was a theoretical success (his conclusions were later made more rigorous by Pippenger [15]) the overhead of repeating each individual computing elements is high. In subsequent decades, solid-state technologies allowed gates and wires to not only shrink, but become orders of magnitude more reliable. Indeed, modern transistors produced using photolithography are expected to operate many trillions of times before failing. As such, von Neumann style repetition is unnecessary.

Only now, as digital circuits continue to shrink, is the reliability of logic gates once again becoming a major cause for concern. The near-term viability of nanoscale architectures is closely tied to whether or not transient faults can be tolerated more efficiently than through simple repetition. After all, if many redundant copies of each nanoscale gate are called for, these copies could simply be replaced with a single lithographically produced CMOS gate.

Fortunately there is reason for optimism. Biological systems, for example the brain, demonstrate a significant level of fault-tolerance but do not appear to embody von Neumann style repetition. More concretely, von Nuemann's approach to reliable computation contrasts sharply with results from digital communication theory. Since the time of Claude Shannon, it has been known that repetition is a highly inefficient error control mechanism when encoding data. To achieve fault-

tolerant communication, a reliable encoder and decoder are used to send information across a noisy channel. When data is encoded in an error-correcting code, information about each input is effectively "spread" across check symbols. By allowing each transmitted check symbol to be a function of many information symbols, only a constant factor overhead is required to protect against random bit flips. Error-correcting codes have been embraced not only to transmit data, but to store data. It is only natural to ask whether similar ideas can be applied to reliable computation. This question is explored in Chapter 9, which presents a framework for computing using error-correcting codes.

### 1.2 Fundamental Characteristics of Nanoscale Computing

This section highlights the major challenges novel modeling and analysis must address in order for nanoscale computing to succeed. As was already noted in the opening paragraph of this thesis, emerging nanoscale computing technologies necessitate fundamental changes in the way computer architectures are designed and analyzed. Significant uncertainty is associated with the assembly and operation of nanoscale devices. This uncertainty must not only be modeled and accounted for, but actively embraced as part of the design process. This is in stark contrast with today's VLSI, where complex, meticulously optimized designs are realized through a deterministic, top-down etching process. For emerging nanoscale architectures, probabilistic modeling and analysis are primary requirements for the successful realization of nanoscale computer architectures.

Listed below are four fundamental ways in which emerging nanoscale computing technology differs from today's VLSI. In each case, we note the consequences with regard to modeling, analysis and design.

### 1.2.1 Stochastic Assembly

Assembly of VSLI technology has traditionally been viewed as deterministic. A circuit is designed, it is realized via a series of masks, and, in principle, each copy of the circuit produced by those mask is identical. As feature sizes have shrunk, however, more and more device-to-device variation has begun to appear. Consequently, circuit designers now see a need to take this variation into account in order to avoid defects.

Emerging nanoscale computing technologies are expected to produce large-scale architectures through a bottom-up assembly process. Such a process, in which nanoscale devices are deposited onto a chip in a directed fashion, potentially increases device-to-device variation by many orders of magnitude more. Designers will need to expect variation not only in the placement and functionality of devices, but also in how they interconnect.

In order to reliably manufacture nanoscale architectures, randomness can no longer be viewed as merely the potential for defects. Instead, it must be accepted as an expected occurrence. It must be anticipated, modeled, and embraced by design. Consequently, probabilistic analysis must be brought to the forefront of the design process.

#### 1.2.2 Post-Assembly Testing and Configuration

A stochastic nanoscale assembly process will yield large amounts of device-to-device variation, and a significant number of permanent defects. To cope with this variation, nanoscale architectures will need to be configured post-assembly. This introduces a new architectural requirement, namely, chips must be configurable so as to provide consistent functionality despite faults and variations in layout.

Today's VLSI already requires testing to verify that chips are working properly. Nanoscale architectures, however, will require testing simply to allow chips to work properly. Architectures will need to be designed such that information about their internal interconnect and the locations of internal faults can be discovered efficiently. Once determined, relevant information will need to be supplied to the many configurable components on each chip. Ideally, this entire process will remain simple enough so that chips can test and configure themselves.

#### 1.2.3 Strict Assembly Constraints

VLSI is manufactured using photolithography, allowing complex circuit designs to be repeatedly reproduced by shining light through a mask. Although these masks are very expensive to produce, they act as reusable templates in VLSI's top-down assembly. In contrast, emergent nanoscale architectures are expected to be assembled from the bottom-up, which implies that no reusable blueprint will be available. Instead millions of nanoscale devices will be grown en masse, then deposited onto a chip in a directed fashion.

At least in the near term, it is not anticipated that the deposited devices will be able to be arranged into arbitrary patterns. Instead they will be deposited to form relatively simple structures that are locally regular. For example, photolithography can still be used to define different regions on a chip, but within each region, nanoscale devices may be organized into nanowire crossbars. The highly regular crossbars would then be configured, or programmed, after assembly, not unlike today's programmable logic arrays. In this way, post-assembly configuration provides otherwise homogenous hardware with the additional nanoscale structure required to perform useful computations.

#### 1.2.4 Imperfect Operation

The success of VLSI has relied heavily on the extremely high reliability of transistors, and hence logic gates. As feature sizes shrink, maintaining this level of reliability has become quite challenging. The problem is only expected to get worse as features shrink to the nanoscale. First, nanoscale devices may be much more likely to break over time. Second, even when operating correctly, they will likely be susceptible to transient errors.

A logic gate that outputs an incorrect value one time in a billion would be completely unacceptable in the context of today's circuit designs. This places an enormous burden on developing nanoscale technology. While it would be ideal if these technologies operated with perfect reliability, near perfect reliability may be much easier to achieve. If we can design circuits that are capable of tolerating gate errors, and algorithms that are capable of tolerating circuit errors, nanoscale

computing will be significantly easier to implement.

### 1.3 An Overview of this Thesis

Chapter 2 describes four broad categories of emergent nanoscale computing technology, followed by a more detailed description of the nanowire crossbar. Chapter 3 provides a detailed look at how nanowire crossbars can be interfaced with existing technology using a device called a "nanowire decoder". In Chapter 3 a range of potential decoder technologies is described and modeled. Using this model, Chapters 4, 5 and 6 analyze the resources required to construct three different types of nanowire decoders; randomized-contact decoders, encoded nanowire decoders, and masked-based decoders. A summarizing comparison of all three decoder types is given at the end of Chapter 6. Chapter 7 considers how decoder requirements change when they are used to control crossbar-based logic as opposed to a memories. Chapter 8 looks at the post-assembly testing that stochastically assembled nanowire decoders require. Chapter 9 investigates how nanoscale architectures can cope with transient faults using error-correcting codes. Chapter 10 provides additional examples of the promise and challenges of code-based fault-tolerance. Finally, a concluding summary of the entire thesis is provided in Chapter 11

### Chapter 2

# Overview of Nanoscale Computing

The first half of this chapter, Section 2.1, presents four broad categories of up-and-coming nanoscale computing technology; nanoscale semiconductor-based architectures (Subsection 2.1.1), DNA-based assemblage (Subsection 2.1.2), Quantum Dot Cellular Automata (Subsection 2.1.3), and Biological Computing (Subsection 2.1.4). In each case, we highlight how the technology embodies the fundamental characteristics of nanoscale computing outlined at the end of the previous chapter.

The second half of this chapter, Section 2.2, provides a more detailed description of semiconductor-base nanowire crossbars. Nanowire crossbars are seen as the current frontrunner for near-term nanoscale architectures and are the focus of much of the research presented in subsequent chapters. Also, since a range of crossbar-related technology has already been demonstrated, they provide the opportunity for practical and realistic models that simultaneously illustrate the fundamental challenges faced by nanoscale computing.

### 2.1 Technology Overview

Broadly speaking, emergent nanoscale computing technology can be placed into four categories: nanoscale semiconductor-based architectures, DNA-based assemblage, quantum-dot cellular automata (QCAs), and biological computing. Each of these categories is described below.

### 2.1.1 Nanoscale Semiconductor-Based Architectures

Today's architectures are based on CMOS technology, which relies on doped silicon (a semiconductor) to implement transistor-based logic. A seemingly natural path toward nanoscale computing would be to continue the downward scaling of today's CMOS devices. Unfortunately, the physical constraints of photolithography makes this extremely challenging, if not impossible. As a result, a number of alternative methods for manufacturing semiconductor-based architectures are being pursued.

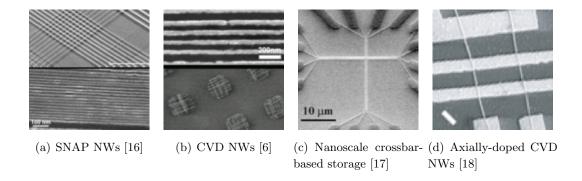

Nanoscale silicon and germanium wires have been produced, and methods for doping these nanowires (NWs) have been demonstrated, as have individual nanoscale devices (e.g. diodes, field-effect transistors and memory cells) [19, 4] (see Figure 2.1). As explained in Section 2.2 below, these devices can then be organized into large-scale architectures via crossbars (i.e. grids) of NWs. Such

Figure 2.1: A range of semiconductor-based nanoscale computing technologies have already been demonstrated. (a) Uniform semiconducting nanowires have been produced by Heath et al at Caltech using a process known as SNAP [16]. (b) Lieber et al at Harvard have used chemical vapor deposition (CVD) to grow nanowires off chip, then deposit them fluidically in parallel [6]. (c) Molecular storage devices have been demonstrated by Williams et al at Hewlett-Packard [17] capable of storing bits at nanowire crosspoints (d) CVD nanowires can be grown with heavily and lightly doped regions along their axis, allowing them to form field-effect transistors with orthogonally placed lithographically produced mesoscale wires [18].

crossbars offer a promising basis for both nanoscale memories (see Section 2.2.2) and programmable logic (see Section 2.2.3).

Even with NW crossbars as a building block, it remains a significant challenge to understand how millions, or billions of nanoscale devices can be organized into general purpose nanoscale architectures. Nanoscale manufacturing constraints, along with significant amounts of device variation make the direct realization of existing chip designs infeasible. Instead new designs and accompanying analysis are required to accommodate the assembly constraints of emerging nanoscale semiconductor-based technologies. The design and analysis of semiconductor-based NW crossbars is the primary focus of this thesis.

#### 2.1.2 DNA-Based Assemblage

In 1994 Adleman observed that carefully selected strands of DNA, assembled in vitro, could be used to carry out arbitrary computations [20]. His key insight was that the sequence of nucleotides on each strand of DNA, which determines which other strands it will bind with, can be viewed as a logical constraint. There are only certain allowed ways in which large, multi-strand sequences can form when many copies of each stand are placed in a fluid. By checking for the presence of a particular multi-strand sequence, one is effectively checking whether a certain set of constraints has been satisfied. This allowed Adleman to use DNA to solve a small instance of the HAMILTONIAN PATH problem, albeit with questionable efficiency (DNA-based computing is relatively slow, and requires a large number of strands).

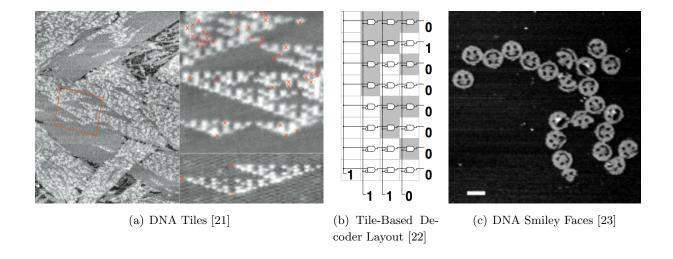

DNA-based computation does not provide a viable alternative to today's computers. What is noteworthy, however, is the ability of DNA to be viewed as a means of programmatically assembling complex structures. Rather than use single strands of DNA, Erik Winfree has demonstrated

Figure 2.2: Strands of DNA with appropriately chosen sequences of amino acids can come together to form complex structures. In (a), nanoscale DNA tiles have assembled to form Sierpinski Triangles [21] (erroneous connections are indicated with red X's). In (b), a hypothetical tile-based decoder circuit is illustrated [22]. In (c) long strands of DNA have been guided by smaller "staple strands" to form multiple copies of an arbitrarily chosen 2D shape [23].

that DNA-based tiles can be manufactured such that they combine to form complex 2D patterns [24] (See Figure 2.2a). Square-shaped abstractions of these tiles have also been the focus of significant theoretical analysis [25, 26, 22, 27] (See Figure 2.2b) as they represent a valuable stochastic generalization of traditional "Wang Tiles" [28]. Along similar lines, Rothemund has studied, and demonstrated, how a long strand of DNA can be directed to fold into arbitrary 2D shapes using a set of carefully chosen "staple strands" (see Figure 2.2c) [23].

The appeal of DNA-based assembly is that a wide range of complex 2D, and even 3D structures can be assembled systematically, thus allowing for a wide range of nanoscale designs. The shortcoming, however, is that the structures themselves cannot be used for computation (they are just static structures). Ideally, computationally functional components could be attached to the DNA, allowing the DNA to act as a scaffolding on which, say, a nanoscale semiconductor-based architecture could be assembled. Unfortunately, the ability to attach DNA to semiconductor-based logic remains undemonstrated. As such, DNA's immediate role in nanoscale computing appears limited.

### 2.1.3 Quantum-Dot Cellular Automata

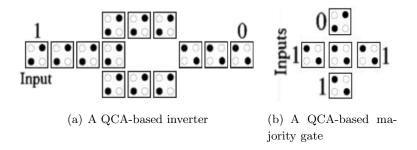

The term "Quantum-dot cellular automata", or QCA, refers to a system of cells in which each cell influences its neighbors via quantum effects. If the cells are properly arranged, they can emulate traditional logic circuits (i.e. implement wires and logic gates, see Figure 2.3) [29, 30]. Although quantum effects are used to compute, the computation being performed is classical (although QCAs capable of performing quantum computation have also been proposed [31]). Since QCAs do not rely on currents or voltages to compute, they have the potential to operate at significantly lower

Figure 2.3: In a QCA, the state of each cell influences the states of its neighbors. To compute, the state of one or more input cells is held fixed while their influence propagates. In the above figures, the black dots contained within each cell exert a repulsive force on each other, and on the dots of neighboring cells. In (a) a QCA-based inverter is illustrated in which a row of cells acts as wires and a forking path along that wire serves to invert the state being transmitted. In (b) whichever three input cells are designated as inputs exert their influence over the center cell. The state of that cell is the propagated to the output. (The above figures are modified from http://www.ece.neu.edu/~mottavi/research.htm)

power and higher densities than today's CMOS.

Although QCAs offer a nanoscale alternative to semiconductor-based logic, there is currently no means of actually assembling and arranging large scale ensembles of nanoscale quantum-dot cells. As such, much quantum-dot research has focused on the simulation and layout of nanoscale quantum-dot circuits. These hypothetical QCA circuits typically rely on complex and irregular arrangements of cells. Unless a means of fabricating QCA-based circuits is developed that allows for a wide range of nanoscale features, nanoscale QCA architectures cannot be realized.

#### 2.1.4 Biological Computing

A very different approach to nanoscale computing involves the use of biological systems, for example, in vivo protein production. This is not viewed as an alternative to traditional computing, but rather an additional domain in which nanoscale computing is anticipated. Within a cell, one protein can promote another protein, which can in turn suppress other proteins. These dependencies can be modeled as a "biological circuit" capable of implementing general logic [32, 33]. The inherent volatility of these systems, however, poses a substantial design challenge, as does the fact that they are being carried out within a living cell.

### 2.2 Nanowire Crossbars

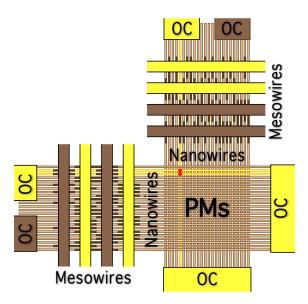

All four of the above categories exhibit fundamental characteristics of nanoscale computing, but the modeling and analysis of future chapters focuses on semiconductor-based nanowire (NW) crossbars (see Figure 2.4). A significant range of crossbar-related technology has already been demonstrated. As a result, NW crossbars are viewed as offering the greatest current promise for nanoscale computing. This section provides an overview of NW crossbar technology and explains how crossbars

Figure 2.4: A crossbar formed from two orthogonal sets of NWs with programmable molecules (PMs) at the crosspoints defined by intersecting NWs. NWs are divided into groups by connecting them to ohmic contacts (OCs). To address a NW in one dimension, an OC is activated and mesoscale wires are used to turn off all but one NW in that group (see Figure 2.5). Data is stored at a crosspoint by applying a large electric field across it. Data is sensed with a smaller field.

can serve as both memories and programmable logic.

#### 2.2.1 Crossbar Assembly

Multiple approaches have been demonstrated for manufacturing NWs for use in crossbars. One method, known as nanoimprint lithography, effectively stamps a set of parallel undifferentiated (i.e. identical) NWs onto a chip [34]. A related method, termed SNAP, also transfers a pattern of undifferentiated NWs onto a chip [16]. A third, more distinct approach, grows many types of differentiated NWs (i.e. NWs comprised of different sequences of materials) off chip, collects the NWs in a large ensemble, then deposits them onto the chip fluidically [35, 36]. Once deposited, both undifferentiated and differentiated NWs can interface with today's photolithographically produced technology (see Chapter 3).

A NW crossbar is formed by depositing a layer of molecular devices between two orthogonal sets of parallel NWs. At each NW crosspoint, this device layer prevents the two orthogonal NWs from coming into direct contact. Instead the NWs are each connected to opposite ends of what is effectively a two-terminal device across which they may apply an electric potential. One promising two-terminal device is a molecular diode that switches between states of low and high resistance in the presence of a sufficiently large positive or negative electric field [37, 38]. A layer of amorphous silicon has also been proposed as a nanoscale programmable medium [39]. Molecular devices that do not behave like diodes (e.g. programmable resistors and transistors) have been considered as well [19, 40]. Comparisons between these alternatives with regard to their information storage

capacity and ability to provide control over NWs can be found in [41, 42, 43].

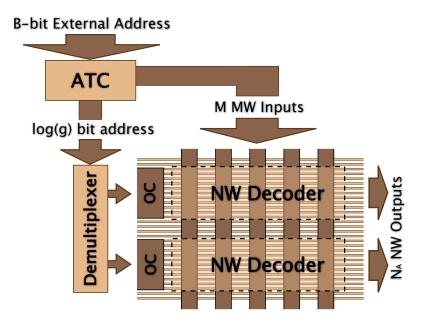

Once a NW crossbar is assembled, g photolithographically produced ohmic contacts (OCs) and M photolithographically produced MWs are placed along each dimension of the crossbar (see Figure 2.4). Each OC is in electrical contact with a group of N consecutive NWs. As such, the OCs allow voltages to be applied to blocks of NWs, while each MW provides control over (i.e. makes nonconducting) subsets of NWs within each block. These subsets, however, cannot be chosen deterministically. Instead, the subsets are determined by a stochastic assembly process. As covered in Section 3.2, a number of methods have been proposed for stochastically coupling MWs to NWs. When a MW is turned on during crossbar operation all of the NWs it controls are turned off. This effectively disconnects any molecular devices to which they are connected.

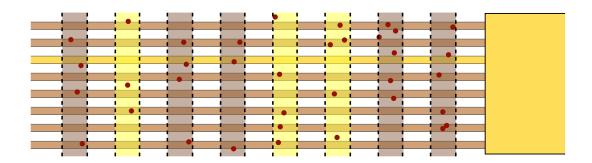

The interface between NWs and MWs is called a **nanowire decoder**, A **simple nanowire decoder** is one in which all NWs are connected to a single OC. A **compound NW decoder** consists of g simple decoders, arranged in parallel (i.e. side by side), which share a common set of MWs (see Figure 2.4). In a compound NW decoder, we sometimes refer to the N NWs within one of the g simple decoders (i.e. the N NWs connected to one of the g OCs) as a **contact group**. A more detailed description of compound versus simple decoders is given in Section 3.1.3.

A NW decoder is said to **address** a particular set of NWs if all NWs in the set remain conducting, or on, while all other NWs are nonconducting, or off. A NW is said to be **individually addressed** if it remains on while all other NWs are off. A more precise definition of what it means to address one or more NWs is given in Section 3.1. If a NW is individually addressed, the OC it is connected to is turned on along with all MWs that *do not* control that NW. As explained in Chapter 3, MWs are coupled to NWs stochastically during NW assembly, and thus not all NWs will be individually addressable.

When NWs along each dimension of a NW crossbar are addressed, the molecular devices at their crosspoints can be accessed and controlled. To accomplish this, the OCs connected to the addressed NWs are used to place either a small or large potential across just the devices being accessed. Since all other NWs are off, the devices located at other NW crosspoints are unaffected. The current flowing across the devices being accessed can also be measured. As we now explain in Sections 2.2.2 and 2.2.3, this combination of addressing NWs via MWs and applying electrical potentials via OCs allows both storage and logic operations to be performed.

#### 2.2.2 Crossbar-based Memories

When many NWs along each dimension of the NW crossbar are addressable, the crossbar can function as a memory (see Figure 2.5). In the crossbar-based memory, read and write operations are executed as follows:

• In a write operation, the molecular diodes at NW crosspoints are addressed by creating a sufficiently large potential between one or more addressed pairs of orthogonal NWs. To apply this potential, the OCs at ends of the NWs in each dimension apply the same voltage. This in turn applies a voltage across the crosspoints being addressed, the polarity of which determines their resistive state. By setting the resistive state of a molecular diode to either high or low, a bit of data is written.

Figure 2.5: A crossbar-based memory in which OCs and MWs read and write data to programmable molecules at crosspoints. The darkened segments along each NW indicate lightly doped regions. These regions become nonconducting when the adjacent MW is turned on. In a read operation an OC at each end of a NW is disconnected from ground. Current flows through any conducting NW crosspoints that are addressed by MWs. The amount of current reveals the value stored at the crosspoints. In a write operation, NWs along each dimension apply a larger electric field across their crosspoints. The direction of the field determines the value stored at the crosspoints. In this figure, the same bit of information is stored at two crosspoints.

• In a **read operation**, crosspoints are again addressed using pairs of NWs. A smaller potential is placed across the crosspoints, preserving their state, and allowing their conductivity to be measured. In the read operation, the addressed NWs in each dimension are disconnected from one of their OCs. As a result, current flows through the crosspoint. The amount of current reveals the resistance of the crosspoint, and hence the value being stored.

### 2.2.3 Crossbar-based Logic

A read operation can potentially be used to read from multiple crosspoints at once, which, as described below, provides a basis for programmable logic by performing WIRED-ORS. In the context of crossbar-based logic, the NWs along one dimension of a crossbar are called "input NWs", and the NWs along the other dimension are called "output NWs". The output NWs from one crossbar can be supplied as input NWs to a second crossbar (see Figure 2.6).

Consider a NW crossbar memory in which a set S of input NWs are addressed. Notice that any output NW that is connected to one of these inputs via a conducting crosspoint (i.e. a crosspoint that stores a "1") will carry a current. In this sense, each output NW performs a WIRED-OR on whichever input NWs are connected to it. In other words, each output NW carries a 1 if and only if at least one of the input NWs connected to it carries a 1. We formalize this below.

• In a wired-or operation, NWs along one dimension of the crossbar serve as inputs and NWs along the other dimension serve as outputs. Molecular diodes connect each input NW to a subset of the output NWs. Multiple input NWs can be addressed, as in a read operation (see above), or alternatively, these NWs can be the current-carrying outputs of another crossbar. In the absence of MW control over the output NWs, any output NW connected to an input NW that carries a current will also carry a current (see Figure 2.6). This allows each output NW to perform a WIRED-OR over the NWs to which it is connected. If MWs are used to address a subset of the output NWs, only those NWs will perform a WIRED-OR. In either case, the current-carrying outputs can serve as inputs to a second crossbar [4].

By supplying the outputs of one crossbar as inputs to another crossbar, multiple logical operations can be carried out. If all of these operations are WIRED-ORS, however, the interconnected crossbars will not be able to implement general logic. Also, signal strength will degenerate because an input NW may drive many outputs. DeHon's proposed solution achieves signal restoration via NW-based field effect transistors (FETs) [4] (see Figure 2.6). Here pairs of orthogonal NWs form FETs, allowing each output NW to be coupled to an input NW such that either an inverter or buffer is formed.

• In a **signal restoration operation**, NWs along one dimension of the crossbar serve as inputs and NWs along the other dimension serve as outputs. Each output NW forms an FET with at most one input NW. OCs are used to apply a voltage across the output NWs. The configuration of the OCs and output NWs determines whether each output computes the NOT of the input NW it forms an FET with, or instead acts as a buffer (i.e. computes the identify function).

Figure 2.6: A level of reconfigurable crossbar-based logic in which a WIRED-OR operation is followed by a signal restoration operation that also implements negation. Light NWs indicate that a boolean value of "1" is being applied, dark NWs indicate a "0". The two operations collectively implement a WIRED-NOR, and thus form a complete basis for boolean logic. The WIRED-OR operation is implemented like a read operation (See Figure 2.5), except that multiple vertical NWs, and all horizontal NWs, are addressed. Any horizontal NW which is connected to an addressed input NW carries a current. The current carrying horizontal NWs then gate (i.e. make nonconducting) a subset of the output NWs using field-effect transistors (FETs). The diode connections used to perform the WIRED-OR operation can be configured via write operations using a NW decoder (not shown), which is disconnected during normal operation. The FETs used to implement the restoration operation may be placed stochastically.

Since nanoscale programmable FET may not be technologically feasible, DeHon has observed that randomly placed FETs can be used to implement this restoration operation [4]. Though promising, the additional overhead associated with stochastic FET placement has not been rigorously analyzed such that manufacturing errors are taken into account.

### Chapter 3

### Nanowire Decoders

The previous chapter summarized how NW crossbars can provide a promising basis for nanoscale memories and programmable logic. This chapter focuses on the specific problem of gaining control over individual NWs. One of the primary requirements for realizing crossbar-based architectures is a method for addressing individual NWs with much larger, lithographically-produced MWs. As explained in Section 2.2.1, this interface between MWs and NWs is referred to as a nanowire decoder.

In this chapter, Section 3.1 provides explicit requirements that NW decoders must meet in order to provide reliable control over memories and logic circuits. Section 3.2 reviews a range of proposed decoder manufacturing technologies, highlighting in each case the stochastic aspects of the decoder's assembly process. Stochastic decoder assembly necessitates post-assembly testing and configuration, which is the focus of Section 3.3. Section 3.4 then describes how the behavior of stochastically-assembled NW decoders can be modeled. The "binary model of nanowire control with errors", defined in Section 3.4.1, is central to the probabilistic analysis presented in subsequent chapters. Section 3.5 provides a framework for this analysis.

### 3.1 Decoder Requirements

In subsequent chapters, we seek to bound the area required to gain control over N NWs using different types of stochastically assembled NW decoders. In this section, we establish the requirements that these decoders must meet in order to provide a sufficient level of control over the NWs. As explained below, the requirements we impose depend on whether the NWs are part of a memory or a circuit.

### 3.1.1 Nanowire Addressing

First we revisit the definition of NW addressing given at the end of Section 2.2.1. Recall that a NW decoder is said to address a set of NWs if all NWs in the set remain conducting, or on, while all other NWs are nonconducting, or off. A NW is said to be individually addressed if it remains on while all other NWs are off. In order for nanoscale architectures to function fast and reliably, the on/off ratio of addressed versus non-addressed NWs should be large. Sometimes we refer to the set of MWs used to individually address a particular NW as that NW's address.

Figure 3.1: On the left, the crosspoint being read has a low resistance, indicating that a "1" is being stored, but all other crosspoints have a high resistance. On the right, however, the crosspoint being read has a high resistance, indicating that a "0" is being stored, but all other crosspoints have a low resistance. To quickly and correctly determine the state of the crosspoint in each case, the amount of current flowing from one dimension of the crossbar to the other must be significantly greater on the left than on the right. This is accomplished only if the on/off ratio of the addressed versus non-addressed NWs is sufficiently large. The same requirement applies to the WIRED-OR portion of crossbar-based logic.

More formally, consider a NW decoder in which each MW, when turned on, increases each NW's resistance by some amount. In this case, we can more formally define what it means for a set of NWs to be addressed as follows [44].

• A set, S, of NWs is **addressed** if and only if a) every NW not in S has a resistance that is at least  $\alpha$  times that of every NW in S and b) the combined resistance of all NWs not in S is at least  $\alpha$  times that of the combined resistance of all NWs in S, where  $\alpha \gg 1$ .

In this definition, condition a) ensures that crossbar write operations function correctly (i.e. it ensures that only the addressed crosspoints get written to), and condition b) ensures that the read operations function correctly (see Figure 3.1). The choice of an actual value of  $\alpha$  is application specific. For example, a larger value would be required to read data from molecular devices with poor on/off ratios. A larger value would also facilitate reading data more quickly and reliably.

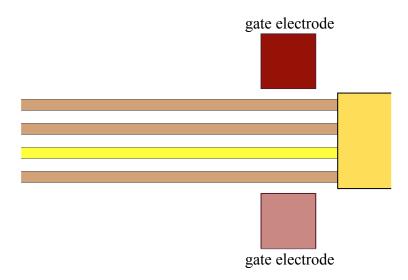

In the context of the above definition, a MW is said to **control** a NW if that MW, when turned on, increases the NW's resistance by a factor larger than  $\alpha$ . A MW is said to **not control** a NW if it increases the NWs resistance by a factor very close to 1 (The phrase "very close" is quantified in Section 3.4.2). If the MW increases the NWs resistance by an intermediate factor, the MW is said to **partially control** the NW.

It is also possible for MWs to control NWs in ways other than increasing their resistance. For example, in a diode-based NW decoder (see Section 3.4.2) each MW is connected to a subset of the NWs via diodes. When a MW is grounded, it provides control over NWs by siphoning current from

the NWs to which it is connected. For this decoder, the word "resistance" in the above definitions is no longer appropriate, but the overall sentiment of the definitions remains applicable. Namely, the combined current carrying capacity of addressed NWs must still be significantly greater than that of the non-addressed NWs. Part of the appeal of the model of decoder behavior introduced in Section 3.4.1 is that it avoids the need to distinguish between different ways in which MWs control NWs.

## 3.1.2 Address Requirements

Having defined what it means for a NW decoder to address a set of NWs, we now establish requirements for the sets themselves. The analysis of subsequent chapters relies on calculating the probability that stochastically assembled decoders fulfill these requirements.

### Nanowire Decoders for Memories

As explained in Section 2.2.2, read/write memory operations are performed in a NW crossbar-based memory by using a NW decoder to address NWs along both dimensions of the crossbar. If the decoders along each dimension are each capable of addressing at least  $N_A$  disjoint sets of NWs, they can collectively control  $(N_A)^2$  disjoint sets of NW crosspoints, each of which can store a bit of information. Since these decoders are comprised of g ohmic contacts (OCs), each of which can be turned on independently,  $N_A = \sum_{i=1}^g N_A^i$ , where  $N_A^i$  denotes the number of disjoint sets of NWs that can be addressed when only the  $i^{th}$  OC is turned on. NW decoders for memories are analyzed in Chapters 4, 5 and 6.

#### Nanowire Decoders for Circuits

A NW decoder may also be used to supply patterns of  $N_A$  inputs to crossbar-based logic circuits. In order to provide a circuit with arbitrary patterns of inputs, it is not sufficient for the decoder to be able to address  $N_A$  disjoint sets of NWs. Instead there must exist a set of  $N_A$  NWs such that all subsets of the NWs are addressable. Such a set is said to be **fully addressable**. NW decoders for logic are analyzed in Chapter 7.

## 3.1.3 Simple Versus Compound Decoders

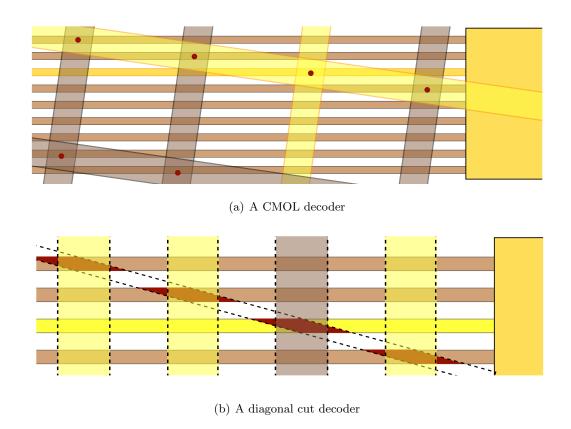

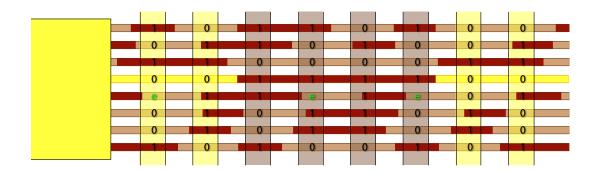

From Section 2.2.1, recall that a simple NW decoder is one in which all NWs are connected to a single OC. A compound NW decoder is g simple decoders, arranged in parallel, that share a common set of MWs (see Figure 3.2). The NWs within a given simple decoder are sometimes referred to as a contact group. Compound NW decoders are well-suited to meeting the addressing requirements of crossbar-based memories, but are less useful in the context of crossbar-based logic.

When a compound NW decoder is used in a crossbar-based memory, dividing the NWs into many contact groups greatly reduces the number of MWs required to address many NWs. The simple NW decoders associated with the g OCs all share the same MWs, but when NWs are addressed only a single OC is turned on at a time. As a result, whether or not a given NW is individually addressable depends only on the NWs within its contact group. This allows us to

Figure 3.2: A compound NW decoder in which two simple decoders are each connected to a different OC, but share a common set of MWs. Since the OCs are controlled by mesoscale circuitry, they can each be turned on or off independently. The NWs within a particular simple decoder are referred to as a contact group.

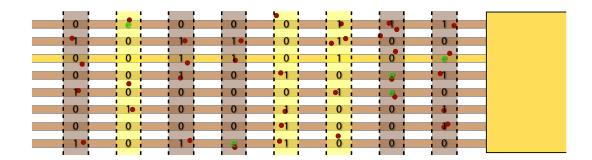

maximize the probability that many NWs are individually addressable by making the number of NWs per OC, N, as small as manufacturing constraints allow. The limits of photolithography suggest that  $N \approx 10$ .