# Nanowire Addressing in the Face of Uncertainty\*

Eric Rachlin and John E. Savage Department of Computer Science Brown University

## **Abstract**

Exploiting the high-potential of nanoscale architectures requires that they be controlled by CMOS technology. Such an interface, a decoder, must control many nanowires (NWs) with a small number of meso-scale wires (MWs). Multiple types of decoder have been proposed, each of which can be modelled as embedding resistive switches in NWs. In this paper we present a general model for NW decoders and use it to specify the criteria they must meet to function correctly and be fault-tolerant. To illustrate the power of our model, we derive the first bounds on the size of a fault-tolerant randomized contact decoder.

## 1 Introduction

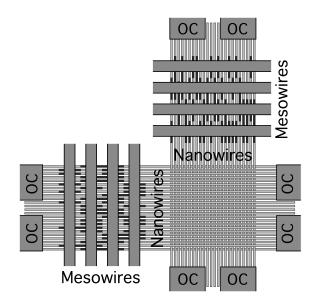

Nanowire-based crossbars constitute a technology with the potential to extend Moore's Law beyond the limits of photolithography. A fundamental challenge in crossbar architectures is providing a reliable means of controlling individual NWs in each dimension with a small number of MWs. A circuit that provides this control is called a NW decoder. (See Figure 1.) These circuits address the general problem of controlling individual NWs. They are applicable to a wide range of architectures.

## 1.1 Nanowire Decoding

Four types of decoder have been proposed. All work on the principle that switchable resistances are created in NWs by the assembly process. The first two, the "randomized contact decoder" and the "randomized mask decoder," work with undifferentiated NWs, NWs that are all the same, except for possible manufacturing defects. Such NWs can be grown on chip using nanoimpring lithography [1, 2] and the superlattice nanowire pattern transfer (SNAP) method [3, 4]. The second two decoders, the "axially-doped

Figure 1. A crossbar with two parallel sets of NWs controlled by mesoscale address wires (MWs). FETs are defined at the intersection of lightly doped (dark) NW regions with MWs. Ohmic contacts (OCs) are made at ends of each set of NWs. Data is stored in the conductivity of molecular switches at crosspoints, intersections of orthogonal NWs.

NW decoder" and the "radially-doped NW decoder," work with differentiated NWs. Different large batches of identical NWs are grown off chip, mixed together, and deposited on chip. In each case the goal is to produce NWs with sections whose resistance can be controlled by fields applied by MWs. The set of MW fields that cause a NW to be conducting is called its **codeword**.

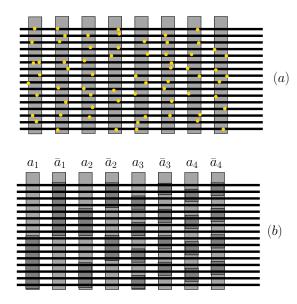

The **randomized contact decoder** [5] scatters particles randomly between NWs and orthogonal MWs, thereby making switcheable resistances at the point of contact between NWs and MWs. (See Figure 2 (a).) A NW is con-

<sup>\*</sup>This research was funded in part by NSF Grant CCF-0403674. To appear in ISVLSI 2006.

Figure 2. (a) A randomized contact decoder and (b) a randomized mask decoder.

ducting only when all its resistances are small. The **randomized mask decoder** [6, 7] interposes lithographically defined high-K dielectric regions, many of which are randomly placed, between MWs and NWs. A high-K dielectric that is adjacent to a MW intensifies its electric field, allowing the MWs to substantially increase the resistance of NWs exposed to the intensified field. (See Figure 2 (b).)

The third decoder, the axially-encoded NW decoder, controls axially differentiated NWs. As NWs grow through chemical vapor deposition, heavily and lightly doped regions are introduced along their axis. When a lightly doped NW region lies under a MW carrying an electric field, the NW's resistance is increased. (See Figure 1.) The fourth decoder, the radially-encoded NW decoder, operates on radially differentiated NWs that are formed by growing differentiably etcheable shells on lightly doped cores. To control these NWs, etching is done in lithographically defined regions to expose the cores of certain NWs to certain MWs, effectively simulating axial encodings.

Differentiated NWs have been assembled on chip using a fluid-based method [8], which aligns NWs in parallel through fluid flow but does not guarantee end-to-end alignment of NWs. Misalignment of axially encoded NW doped regions can lead to ambiguous control of NWs, a problem that doesn't arise with radially encoded NWs.

### 1.2 The General Decoder

We now present our general model for NW decoders. Small sets of NWs are controlled by "simple NW decoders" that are aggregated into "composite NW decoders." Since nanoscale manufacturing is stochastic, simple decoders become difficult to produce when N is large. For this reason, we use composite decoders.

#### **Definition 1.1** *In a* simple nanowire decoder:

- 1. M large MWs control N much smaller NWs. The NWs are tightly packed and (at least partially) aligned, but are not in electrical contact with one another.

- 2. A pair of ohmic contacts applies a voltage across all NWs simultaneously. In the absence of MW control, all NWs conduct, effectively behaving like a single wire.

- 3. Each MW provides control over some subset of the NWs. A MW controls a NW if its resistance increases substantially when that MW carries a voltage.

- 4. When multiple MWs carry a voltage, the resistances induced in a NW are summed. The decoder addresses the NWs with low resistance.

**Definition 1.2** A composite nanowire decoder uses multiple simple NW decoders, each associated with a pair of independently controllable ohmic contacts, to control groups of N NWs. All simple decoders share a single set of MWs, saving a substantial amount of space.

To analyze these NW decoders, we require a model for MW control of NWs. We provide such a model in Section 2 and provide criteria that decoders must meet to function properly. In Section 3 we describe several classes of code that meet these criteria. Section 4 extends our model to cope with real-world manufacturing defects. To conclude, we provide a bound on the size of a fault-tolerant randomized contact decoder.

## 2 NW Codewords

Consider a simple NW decoder with M MW inputs and N NW outputs. Each MW provides control over a subset of NWs. In an **ideal decoder**, a NW is completely turned off (made nonconducting) by applying a field on a controlling MW and unaffected by a noncontrolling MW.

To describe an idealized NW decoder, we associate an M-bit vector (a **binary codeword**) with each NW. Let  $c^i$  be the codeword associated with NW  $n_i$ ,  $1 \le i \le N$ , and let  $c^i_j$  ( $1 \le j \le M$ ) be the  $j^{th}$  bit of  $c^i$ .  $c^i_j = 1$  (0) if and only if NW  $n_i$  is controlled (unaffected) by the  $j^{th}$  MW.

Let a be the M-bit input (**activation pattern**) supplied to the decoder where  $a_j=1$  if and only if the  $j^{th}$  MW carries a voltage. An activation pattern turns off NW  $n_i$  if and only if there exists a j such that  $a_j=1$  and  $c_j^i=1$ . Equivalently, a turns off NW  $n_i$  if and only if  $a \cdot c^i=\sum_{j=1}^M a_j^i c_j^i \geq 1$ , where addition is over the integers.

## 2.1 Random Codeword Assignment

The four decoders described above assign codewords stochastically, a characteristic of all known NW decoders. Although some proposals allow portions of a NW's codewords may be assigned deterministically [9], a stochastic decoder is still needed.

The probability distribution governing the selection of NWs depends on the manufacturing process. This distribution is very important when evaluating decoding technologies. To illustrate this point, we compare the randomized contact and axial decoders when there is no misalignment.

- 1. In an ideal randomized contact decoder, codeword bits are generated independently.  $c_j^i = 1$  with probability p, a parameter of the manufacturing process.

- 2. In an axial decoder codewords are assigned to NWs independently with some fixed probability. In an ideal axial decoder (which is not misaligned),  $c_j^i = 1$  if NW  $n_i$  has a lightly-doped region under the  $j^{th}$  MW. Otherwise  $c_j^i = 0$ . When NWs are deposited, a random subset of axial encodings is selected. Each encoding maps to a codeword. Codeword probabilities are a function of the corresponding encoding's relative concentrations in the original ensemble. Axial decoders are analyzed in [10].

We now show that ideal axial decoding is at least as good as ideal randomized contact decoding (or any decoding method which assigns bits independently at random).

**Theorem 2.1** An ideal axial decoder can simulate an ideal randomized contact decoder by assigning lightly- and heavily-doped regions to NW sections with equal probability while they are grown.

**Proof** If all possible doping patterns are produced with the proper concentrations, bits in an axial decoder will be independent random variables, simulating codeword assignment in a randomized contact decoder.

## 2.2 NW Addressability

We define the criteria codewords in a properly functioning decoder must meet using the binary codeword model.

- 1. Consider two NWs,  $n_a$  and  $n_b$ . If  $c^a$  contains a 1 in every position that  $c^b$  has a 1, it is impossible to turn off  $n_b$  without also turning off  $n_a$ . For this reason, we say  $c^b$  implies  $c^a$ , denoted  $c^b \Rightarrow c^a$ .

- 2. The **complement** of codeword  $c^i$ , denoted  $\overline{c^i}$ , is the NOT of M-bit vector  $c^i$ . If  $c^b \not\Rightarrow c^a$ , activation pattern  $a = \overline{c^b}$  turns off NW  $n_a$ , but not  $n_b$  (since  $\overline{c^b} \cdot c^b = 0$ ). If  $c^b \not\Rightarrow c^a$  and  $c^a \not\Rightarrow c^b$ , NWs  $n_a$  and  $n_b$  are **independently controllable**.

3. A set S of NWs is addressable if there exists an activation pattern that turns off every NW not in S, and no NWs in S. A subset S' of S is addressable with respect to S if there exists an activation pattern that turns off every NW in S - S' and no NWs in S'. A single NW, n<sub>i</sub>, is addressable if the set {n<sub>i</sub>} is addressable. A codeword is addressable if the set of NWs with that codeword are addressable.

To understand the importance of codeword implication, we provide the following lemma.

**Lemma 2.1** A NW  $n_a$  with codeword  $c^a$  is addressable if and only if  $c^i \not\Rightarrow c^a$  for all  $i \neq a$ . A codeword  $c^a$  is addressable if and only if  $c^i \not\Rightarrow c^a$  for all  $c^i \neq c^a$

**Proof** If  $n_a$  ( $c^a$ ) is addressable, an activation pattern, a, exists that turns off all NWs (codewords) other than  $n_a$  ( $c^a$ ). None of these NWs (codeword) imply  $c^a$ . For the converse, recall that if  $c_i \not\Rightarrow c_a$ ,  $a = \overline{c^a}$  turns off  $n_i$ .

Notice that if two NWs are addressable, they are necessarily independently controllable. Also, if all pairs of NWs are independently controllable, every NW is addressable.

#### 2.3 Memory Decoders

NW decoders can be used to control a memory. (See Fig 1.). In a NW crossbar, a composite decoder is used along each dimension to select one or more crosspoints. For the memory to function properly, binary addresses must be mapped to disjoint sets of crosspoints.

A simple NW decoder which can address D disjoint sets of NWs is called a D-address simple memory decoder. Its codewords must meet the following requirement.

**Lemma 2.2** A decoder is a *D*-address simple memory decoder if and only if there exist *D* addressable codewords.

**Proof** If D addressable codewords exist, the NWs with these codewords form D disjoint addressable subsets. For the converse, assume D disjoint addressable subsets of NWs exists. Each set must contain a codeword which no other codeword implies. Since each set is addressable, the D codewords are addressable and also distinct.

In an *N*-address simple memory decoder all NWs, and hence all codewords, must be addressable. This implies that all pairs of NWs are independently controllable. In Section 3 we give the minimum length of such a code.

#### 2.4 Circuit Decoders

A memory decoder must activate disjoint subsets of wires in order to control a memory efficiently. Now consider a decoder that acts as input to a circuit. If the circuit has D inputs, the decoder must provide control over a set S of D NWs. To supply the circuit with all  $2^D$  possible inputs, the decoder must be able to address every subset of S with respect to S. We call such a decoder a D-address circuit decoder and give a condition on its codewords.

**Definition 2.1** Let S be a set of NWs that contains NW  $n_i$ .  $n_i$  is **uniquely controllable** with respect to S if there exists a j such that  $c_j^i = 1$  and  $c_j^a = 0$  for every other  $n_a \in S$ . Here  $a_j$  **uniquely controls**  $n_i$ , with respect to S.

**Lemma 2.3** A decoder is a D-address circuit decoder if and only if there exists a set S of size D such that each NW in S is uniquely controllable with respect to S.

**Proof** If every NW in S is uniquely controllable, there is an  $a_j$  which uniquely controls each  $n_i \in S$ . To turn off a subset of NW S', set  $a_j = 1$  if and only if  $a_j$  uniquely controls a NW in S'. For the converse, assume each subset of S is addressable with respect to S. Since each set  $S - \{n_i\}$  is addressable with respect to S, each NW,  $n_i$ , is uniquely controllable, with respect to S.

Our lemma does not assume a simple NW decoder. The condition on S still holds even if the decoder is composite.

To control N NW inputs to a circuit, we require at least N MWs, which presents an I/O challenge. It also presents a manufacturing challenge, as shown below.

In randomized-mask decoders, each MW controls multiple consecutive NWs. They cannot produce a set of adjacent, uniquely controllable NWs. Axial, radial and random-contact decoders assign codewords to NWs independently, and with fixed probability. In this case, the following holds.

**Theorem 2.2** Consider a NW decoder in which all N NWs are uniquely controllable using M MWs with probability  $(1 - \epsilon)$ . If NWs are assigned codewords independently and with fixed probability,

$$M > e(1 - \epsilon)(N - 1)$$

**Proof** Since probabilities are fixed, the probability than NW  $n_i$  receives a particular codeword is independent of i. Thus  $p_j = Prob(c_j^i = 1)$  is independent of i. It follows that the probability that the  $j^{th}$  MW uniquely controls NW  $n_i$  is  $Q(p_j) = p_j(1-p_j)^{N-1}$ . The probability that the  $j^{th}$  MW controls one of the N NWs is exactly  $NQ(p_j)$  because the N events are disjoint.  $Q(p_j)$  is maximal when  $p_j = 1/N$ . So  $NQ(p_j) \leq (1-1/N)^{N-1} = (N/(N-1))(1-1/N)^N \leq e^{-1}N/(N-1)$ .

Since all N NWs are uniquely controllable with probability  $(1-\epsilon)$ , the expected number of MWs that uniquely control some NW is at least  $(1-\epsilon)N$ . The expected number of NWs controlled by M MWs is at most  $Me^{-1}N/(N-1)$ . Thus,  $M \ge e(1-\epsilon)(N-1)$ .

#### 3 Minimum Code Size

Even when codeword assignment is stochastic, some decoders (axial and radial, for example) provide substantial control over which codewords are generated. Future nanotechnology may even permit codewords to be deterministically programmed. In both cases, we wish to satisfy the conditions established by Lemmas 2.2 and 2.3 using minimum length codewords. In this section we present codes (sets of codewords) that satisfy this condition.

#### 3.1 Codewords for Circuits

In a circuit decoder, Lemma 2.3 requires a set of D uniquely controllable NWs. Each wire must have a distinct codeword and each of these codewords must have a 1 in a unique position. The lemma implies that M, the number of bits in each codeword, is at least D. M = D if and only if codewords are drawn from a (1, D)-hot code. A (k, M)-hot code [11] consists of codewords of length M in which each codeword has k 1s. Thus, a 1-hot code has a single 1 in each of its M codeword.

#### 3.2 Codewords for Memories

In a memory decoder, Lemma 2.2 requires a set of D NWs with distinct codewords, none of which imply other codewords. Given M MWs, we now consider methods for generating length-M codewords in which every codeword is addressable.

First consider binary reflected codes, introduced in [10]. A **binary reflected code** (BRC) is code that contains all length-M codewords of the form  $x\overline{x}$ , where x is an arbitrary binary vector (and M is even).

In our previous work, we have found it convenient to use BRCs because each codeword directly corresponds to a binary sequence, x. (They also have the property that they are closed under cyclic shift, which models misalignment of axial codes.) BRCs and their subsets have also been used by others for the same reason [12, 13].

A BRC contains  $2^{M/2}$  codewords. All pairs of codewords are independently addressable (since no codeword implies another codeword). Unfortunately, they are not optimal in that they use more MWs than some other codes with the same number of codewords.

The  $(\lceil M/2 \rceil, M)$ -hot codes are optimal in their use of MWs, as we show. A (k, M)-hot code contains  $\binom{M}{k}$  codewords. As with BRCs, each codeword is addressable. (They are also closed under cyclic shift.) An  $(\lceil M/2 \rceil, M)$ -hot code has  $\binom{M}{\lceil M/2 \rceil}$  addressable codewords, which is optimal.

**Lemma 3.1** Consider a set of C addressable codewords. The set consisting of the complement of each codeword also contains C addressable codewords.

**Proof** All codewords are addressable if and only if for any pair of codewords,  $c^a \not\Rightarrow \underline{c}^b$  and  $\underline{c}^b \not\Rightarrow \underline{c}^a$ . If  $c^a \not\Rightarrow c^b$  and  $c^b \not\Rightarrow c^a$ , then  $\overline{c^a} \not\Rightarrow \overline{c^b}$  and  $\overline{c^b} \not\Rightarrow \overline{c^a}$ .

**Lemma 3.2** Consider a set of C codewords which are independently addressable. If the minimum weight codeword has weight  $w < \lfloor M/2 \rfloor$ , there exists a code with C' codewords, such that C' > C and all codewords have weight at least w + 1.

**Proof** If  $w < \lfloor M/2 \rfloor$ , replace each w-weight codeword with each of the M-w (w+1)-weight codewords it implies. It can be show that this both increases the size of the code, and maintains the condition that all codewords are independently addressable.  $\blacksquare$

**Lemma 3.3** Consider a set of C codewords which are independently addressable. If all codewords have weight  $\lfloor M/2 \rfloor$  or  $\lceil M/2 \rceil$ , there exists a code with  $C' \geq C$  codewords such that all codewords have weight  $\lceil M/2 \rceil$ .

**Proof** If M is odd, consider the same replacement described in the proof of Lemma 3.2. Now code size may remain unchanged.

**Theorem 3.1** Given M MWs, there exist at most  $\binom{M}{\lceil M/2 \rceil}$  addressable codewords.

**Proof** Consider a code that maximizes the number of codewords. Lemma 3.1 states that the complement of this code also maximizes the number of codewords.

Lemma 3.2 implies that the code and its complement both have minimum weight codewords of weight at least  $\lfloor M/2 \rfloor$ . This means that all codewords in either code have weight  $\lfloor M/2 \rfloor$  or  $\lceil M/2 \rceil$ .

Lemma 3.3 states that an equal size code exists where all codewords have weight  $\lceil M/2 \rceil$ . There are at most  $\binom{M}{\lceil M/2 \rceil}$  such codewords.  $\blacksquare$

## **4 Tolerating Codeword Errors**

Binary codewords describe the behavior of an ideal decoder. In ideal decoders, MWs provide all-or-nothing control over NWs. If NW on/off ratios are large, this is not an unreasonable assumption, although in practice it may be necessary to accommodate defects of various kinds. We do this by modifying our binary model slightly, assuming that some bits can be corrupted by an error. If bit  $c_j^i$  is in error, NW  $n_i$  behaves unpredictably with regard to MW  $a_j$ . To address codeword  $n_i$ , we must not activate MW  $a_j$ . To turn off  $n_i$ , we must activate an  $a_k$  for which  $c_k^i$  is not in error (and equal to 1). If MW  $a_j$  is activated, a MW  $a_k$  must also be activated.

Codewords in BRC and (k, M)-codes are addressable in the absence of errors. If codes tolerate d errors, we can accommodate the following real-world decoder defects.

- 1. After codewords are assigned, d bit flips occur. (This can model etching errors in radial decoders.)

- 2. *d* bits become partially corrupted, no longer behaving as 0s and 1s. (This can model misalignment, doping variation or poor separation between NWs and MWs.)

- 3. *d* transient errors in which a 1 becomes a 0 or is partially corrupted.

Unfortunately, transient errors in which a 0 becomes a 1 (and a NW is turned off incorrectly) cannot be tolerated because even one such error can prevent a corrupted NW from being addressed. Fortunately, these errors may be detectable by measuring the current produced by the decoder.

Two NWs,  $n_a$  and  $n_b$  are independently controllable without errors if  $c^a \not\Rightarrow c^b$  and  $c^b \not\Rightarrow c^a$ .

**Definition 4.1** Two NWs are **d-independently controllable** if they remain independently addressable when up to d bit flips occur in their codewords. A set of NWs is **d-addressable** if every pair of NWs in the set is d-independently controllable.

NWs which are d-independently controllable will be able to tolerate up to d errors. Let  $|\boldsymbol{c^a}-\boldsymbol{c^b}\rangle$  be the number of is for which  $c_i^a=1$  but  $c_i^b=0$ . The **balanced Hamming distance** between  $\boldsymbol{c^a}$  and  $\boldsymbol{c^b}$  is  $2\min(|\boldsymbol{c^a}-\boldsymbol{c^b}\rangle,|\boldsymbol{c^b}-\boldsymbol{c^a}\rangle)$ .

**Lemma 4.1** If all pairs of codewords have a balanced Hamming distance of at least 2d + 2, they are d-independently controllable. In this case, a total of d errors can be corrected. Also, up to d/2 errors in every codeword can be corrected.

**Lemma 4.2** If codewords have a balanced Hamming distance of 2d + 2, they have a normal Hamming distance of at least 2d + 2. Two BRC codewords  $x_1\overline{x_1}$  and  $x_2\overline{x_2}$  have a balanced Hamming distance 2d + 2 if and only if  $x_1$  and  $x_2$  have a normal Hamming distance d + 1.

The last observation allows the  $x_i$  to be codewords from a standard error correcting code. The previous work on fault tolerant NW decoders assumes binary reflected codewords [12] and thus fails to define the more general notion of balanced Hamming distance. This work also does not accurately categorize which codewords are addressable. If errors cause  $c^a \Rightarrow c^b$ , the authors assume neither codeword is addressable. Lemmas 2.1 and 2.2 correct this assumption.

## 4.1 Randomized Contact Decoder

In this section we enforce the condition of balanced Hamming distance for the randomized contact decoder. We give an upper bound on M, the number of MWs required

for all codewords in a randomized contact decoder to have a balanced Hamming distance of at least 2d+2 with probability at least  $1-\epsilon$ . When d=0, the bound simply ensures that all NWs are addressable. A bound on M when d=0 is cited in [5] but gives no mention of  $\epsilon$ .

**Theorem 4.1** All N NWs in a randomized contact decoder (where  $P(c_j^i = 1) = p$ ) are d-addressable with probability at least  $1 - \epsilon$  when the number of MWs M satisfies

$$M \ge \frac{\left(d + \sqrt{d^2 + 4\ln(N^2/\epsilon)}\right)^2}{(4p(1-p))}$$

The bound is  $M \ge \ln(N/\sqrt{\epsilon})/(2p(1-p))$  when d=0.

**Proof** Two NWs  $n_a$  and  $n_b$  are d-independently controllable if their balanced Hamming distance is at least 2(d+1). If NWs  $n_a$  and  $n_b$  are not d-independently controllable, then either  $|c^a-c^b| \leq d$  or  $|c^b-c^a| \leq d$ . Since there are N(N-1) such inequalities, all pairs of NWs are d-independently controllable with probability at least  $1-\epsilon$  when the following condition holds.

$$N(N-1)Pr(|\boldsymbol{c^a} - \boldsymbol{c^b}\rangle \le d) \le \epsilon$$

Let  $x_j = 1$  denote the event  $c_i^a = 0$  and  $c_i^b = 1$ . Then,

$$X = \sum_{i=1}^{M} x_j = |\boldsymbol{c}^{\boldsymbol{a}} - \boldsymbol{c}^{\boldsymbol{b}}\rangle$$

The probability that  $x_j=1$  is q=p(1-p). The bound  $P(X\leq d)\leq e^{-MqE(\theta)}$  is given in [10, Lemma A.3] when  $d=\theta Mq$  and  $E(\theta)=(1-\theta+\theta\ln\theta)$ . We must choose M so that  $N^2P(X\leq d)\leq \epsilon$ . Since  $(Mq)E(d/Mq)\geq Mq-d\ln(Mq)$ , our condition on M holds when  $Mq-d\ln Mq\geq \ln(N^2/\epsilon)$ . Because  $Mq\geq 1$ , we can impose an even stronger condition and replace  $\ln Mq$  by  $\sqrt{Mq}$ . This gives the inequality  $Mq-d\sqrt{Mq}\geq \ln(N^2/\epsilon)$ . This is a quadratic inequality satisfied when  $4Mq\geq \left(d+\sqrt{d^2+4\ln(N^2/\epsilon)}\right)^2$ .

## 5 Conclusions

We introduce the binary codeword model, permitting a general discussion of NW decoders. We specify criteria decoders must satisfy and describe codes that meet these criteria. We also introduce balanced Hamming distance which characterizes fault-tolerant decoders. To illustrate the utility of our work, we derive a bound on the number of MWs required to create a fault-tolerant random contact decoder.

#### References

- S. Y. Chou, P. R. Krauss, and P. J. Renstrom. Imprint lithography with 25-nanometer resolution. *Science*, 272:85–87, 1996.

- [2] W. Wu, G. Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, William M. Tong, S.-Y. Wang, J. A. Liddle, W. M. Tong, and R. Stanley Williams. One-kilobit cross-bar molecular memory circuits at 30nm half-pitch fabricated by nanoimprint lithography. *Applied Physics A*, 80:1173–1178, 2005.

- [3] Nicholas A. Melosh, Akram Boukai, Frederic Diana, Brian Gerardot, Antonio Badolato, Pierre M. Petroff, and James R. Heath. Ultrahigh-density nanowire lattices and circuits. *Science*, 300:112–115, Apr. 4, 2003.

- [4] E. Johnston-Halperin, R. Beckman, Y. Luo, N. Melosh, J. Green, and J.R. Heath. Fabrication of conducting silicon nanowire arrays. *J. Applied Physics Letters*, 96(10):5921– 5923, 2004.

- [5] R. S. Williams and P. J. Kuekes. Demultiplexer for a molecular wire crossbar network, US Patent Number 6,256,767, July 3, 2001.

- [6] Eric Rachlin, John E Savage, and Benjamin Gojman. Analysis of a mask-based nanowire decoder. In *Procs 2005 Int. Symp. on VLSI*, Tampa, FL, May 11-12, 2005.

- [7] Robert Beckman, Ezekiel Johnston-Halperin, Yi Luo, Jonathan E. Green, and James R. Heath. Bridging dimensions: Demultiplexing ultrahigh-density nanowire circuits. *Science*, 310:465–468, 2005.

- [8] Y. Huang, X. Duan, Q. Wei, and C. M. Lieber. Directed assembly of one-dimensional nanostructures into functional networks. *Science*, 291:630–633, 2001.

- [9] André Dehon. Deterministic addressing of nanoscale devices assembled at sublithographic pitches. *IEEE Transactions on Nanotechnology*, 4(6):681–687, 2005.

- [10] Benjamin Gojman, Eric Rachlin, and John E. Savage. Evaluation of design strategies for stochastically assembled nanoarray memories. *J. Emerg. Technol. Comput. Syst.*, 1(2):73–108, 2005.

- [11] André DeHon, Patrick Lincoln, and John E. Savage. Stochastic assembly of sublithographic nanoscale interfaces. *IEEE Transactions on Nanotechnology*, 2(3):165–174, 2003.

- [12] Philip J Kuekes, Warren Robinett, Gabriel Seroussi, and R Stanley Williams. Defect-tolerant interconnect to nanoelectronic circuits. *Nanotechnology*, 16:869–882, 2005.

- [13] Philip J Kuekes, Warren Robinett, and R Stanley Williams. Improved voltage margins using linear error correctingcodes in resistor-logic demultiplexers for nanoelectronics. *Nanotechnology*, 16:1419–1432, 2005.

- [14] H. Chernoff. A measure of asymptotic efficiency for tests of a hypothesis based on a sum of observations. *Ann. Math. Stat.*, 23:493–507, 1960.