**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

#### The Theory and Practice of I/O-Efficient Computation

by

Darren Erik Vengroff

B.S.E. Princeton University, 1989

Sc.M. Brown University, 1993

#### Thesis

Submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in the Department of Computer Science at Brown University.

UMI Number: 9738639

Copyright 1997 by Vengroff, Darren Erik

All rights reserved.

UMI Microform 9738639 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

© Copyright 1997

by

Darren Erik Vengroff

# This dissertation by Darren Erik Vengroff is accepted in its present form by the Department of Computer Science as satisfying the dissertation requirement for the degree of Doctor of Philosophy.

Date 4/12/97 Alfay Scott Vitter

Recommended to the Graduate Council

Date 4/22/97 Photo Com

Roberto Tamassia

Date 4/16/97 Thomas H. Comen

Thomas H. Cormen

Approved by the Graduate Council

This thesis is dedicated to the memory of Paris C. Kanellakis. He was a teacher, a colleague, and a friend.

Paris' untimely death in December of 1995 touched all of Computer Science. More importantly, however, we were touched by his remarkable life, and are better for having been.

# Acknowledgments

First and foremost, I thank my wife, Hilary Hoover, for her constant support and encouragement during the years I spent researching and writing this thesis. During that time we followed one another's careers back and forth across the country-from Seattle to Storrs, to Providence, Boston, Durham, and Ann Arbor, back to Seattle, and back to Ann Arbor. Through it all, Hilary has always been there whenever I needed her.

I also received a tremendous amount of support and encouragement from my parents Linda and Richard, my stepmother Cindy, and my sisters Lisa and Marriah. Their expectations of success have always been the highest but their love and understanding have always remained unconditional.

I thank Jeff Vitter, my advisor, for first pointing me towards I/O and for guiding me along the path that led to this thesis. The other present and former members of my thesis committee, Roberto Tamassia, Tom Cormen, and the late Paris Kanellakis also provided many helpful comments and suggestions, both on my early work and on this thesis itself.

Many colleagues contributed to the development of the ideas presented herein. Some of these were co-authors on papers in which many of the ideas in this thesis were originally presented. These include Lars Arge, Yi-Jen Chiang, Mike Goodrich, Eddie Grove, Jyh-Jong Tsay, Roberto Tamassia, and Jeff Vitter. Others who provided helpful technical discussions of various aspects of the work include Rakesh Barve, Tom Cormen,

Philip Klein, David Kotz, Peter Bro Miltersen, T. M. Murali, Mark Nodine, John Savage, Elizabeth Shriver, and Len Wisniewski.

During my time as a graduate student, I had the opportunity to travel extensively outside of Brown, both in physical space and in cyberspace. I was graciously hosted by a number of individuals and institutions, including the Department of Computer Science at Duke University, Yale Patt and the HPS group in the Department of Electrical Engineering and Computer Science at the University of Michigan, Ed Lazowska and the Department of Computer Science and Engineering at the University of Washington, Mitch Alsup and Eric Sprangle at Ross Technology, and Tom Cormen and David Kotz at Dartmouth College.

In addition to my official hosts during my travels I had a number of unofficial hosts who generously opened their homes to me. These include T. M. Murali, and Jeff, Sharon, Jillian, Scott, and Audrey Vitter in Durham, and Eric Sprangle and David, Amy, Alexander, and Evan St. Angelo in Austin.

Last, but certainly not least, I thank all those who helped me successfully navigate the administrative and financial seas one must inevitably cross to complete a Ph.D. These include Mary Andrade, Trina Avery, Dawn Nicholaus, and Jennet Kirschenbaum at Brown, Cathie Caimano, Ellen Denham, the late Anna Drozdowski, Tina Gaither, Sondra Haithcock, Denita Thomas, and Kathleen Williams at Duke, and Michelle Chapman at Michigan.

# Contents

| A | ckno | owledgments                                  | iv |  |  |  |

|---|------|----------------------------------------------|----|--|--|--|

| Ι | Fu   | ndamentals                                   | 1  |  |  |  |

| 1 | Int  | Introduction                                 |    |  |  |  |

|   | 1.1  | Hierarchical Memory                          | 3  |  |  |  |

|   | 1.2  | A Brief History of I/O-efficient Computation | 5  |  |  |  |

|   | 1.3  | Related Work                                 | 7  |  |  |  |

|   |      | 1.3.1 Algorithmics                           | 7  |  |  |  |

|   |      | 1.3.2 I/O-Efficient Computation Systems      | 8  |  |  |  |

|   | 1.4  | Contributions of this Thesis                 | 13 |  |  |  |

| 2 | Mo   | dels and Mathematical Preliminaries          | 16 |  |  |  |

|   | 2.1  | Modeling the Behavior of Disks               | 16 |  |  |  |

|   | 2.2  | The I/O Model of Computation                 | 18 |  |  |  |

|   | 2.3  | The Parallel Disk Model                      | 20 |  |  |  |

|   | 2.4  | Paradigms of I/O-Efficient Computation       | 23 |  |  |  |

|   |      | 2.4.1 Scanning                               | 23 |  |  |  |

|   |      | 2.4.2 Distribution and Merging               | 26 |  |  |  |

|   |      | 2.4.3 Block Linking and Meta-data            | 29 |  |  |  |

| 3  | Pe                       | rmutat                   | mutation and Sorting 32                                     |    |  |

|----|--------------------------|--------------------------|-------------------------------------------------------------|----|--|

|    | 3.1                      | Lower                    | Lower Bounds: Linear Complexity vs. Permutation Complexity  |    |  |

|    | 3.2                      | Sortin                   | Sorting                                                     |    |  |

|    | 3.3                      | Comp                     | paring Independent Disk Sorting and Striped Disk Sorting    | 37 |  |

|    |                          |                          |                                                             |    |  |

| I  | I A                      | lgoritl                  | hms                                                         | 40 |  |

| 4  | Combinatorial Algorithms |                          |                                                             | 41 |  |

|    | 4.1                      | 4.1 Geometric Algorithms |                                                             |    |  |

|    |                          | 4.1.1                    | Distribution Sweeping, a Generalization of Plane Sweeping   | 42 |  |

|    |                          | 4.1.2                    | Batch Filtering                                             | 54 |  |

|    |                          | 4.1.3                    | Convex Hull Algorithms                                      | 60 |  |

|    | 4.2                      | Graph                    | n-Theoretic Algorithms                                      | 64 |  |

|    |                          | 4.2.1                    | PRAM Simulation                                             | 65 |  |

|    |                          | 4.2.2                    | Generic Simulation of an $O(N)$ Space PRAM Algorithm        | 65 |  |

|    |                          | 4.2.3                    | Simulation of Super-Linear Space PRAM Algorithms            | 67 |  |

|    |                          | 4.2.4                    | Reduced Work Simulation for Geometrically Decreasing Compu- |    |  |

|    |                          |                          | tations                                                     | 68 |  |

|    | 4.3                      | List R                   | anking                                                      | 70 |  |

|    | 4.4                      | Conclu                   | usions                                                      | 72 |  |

| 5  | Alg                      | orithm                   | s for Scientific Computation                                | 74 |  |

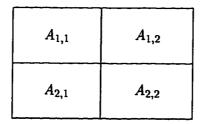

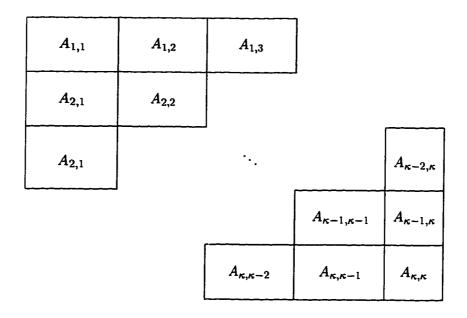

|    | 5.1                      | Sparse                   | Matrix Methods                                              | 74 |  |

|    | 5.2                      | Dense                    | Matrix Methods                                              | 78 |  |

|    |                          |                          |                                                             |    |  |

| II | II                       | PIE                      |                                                             | 87 |  |

| 6  | TPI                      | E, a T                   | ransparent Parallel I/O Environment                         | 88 |  |

|    | 6.1                      | The St                   | ructure of TPIE                                             | 20 |  |

| 6.2 | Stream   | ms                                              |  |

|-----|----------|-------------------------------------------------|--|

| 6.3 | Scanning |                                                 |  |

|     | 6.3.1    | Basic Scanning                                  |  |

|     | 6.3.2    | ASCII Input/Output                              |  |

|     | 6.3.3    | Multi-Type Scanning                             |  |

|     | 6.3.4    | Out-of-Step Scanning                            |  |

| 6.4 | Mergi    | ng                                              |  |

|     | 6.4.1    | Implementing Mergesort: An Extended Example 104 |  |

| 6.5 | Distri   | bution                                          |  |

| 6.6 | Permu    | ntation                                         |  |

|     | 6.6.1    | General Permutation                             |  |

|     | 6.6.2    | Bit Permutation                                 |  |

| 6.7 | Sortin   | g                                               |  |

|     | 6.7.1    | Comparison Sorting                              |  |

|     | 6.7.2    | Key Bucket Sorting                              |  |

| 6.8 | Matrix   | Operations                                      |  |

|     | 6.8.1    | Dense Matrix Operations                         |  |

|     | 6.8.2    | Sparse Matrices                                 |  |

|     | 6.8.3    | Element-wise Arithmetic                         |  |

|     | 6.8.4    | Sparse Matrix by Vector Multiplication          |  |

| 6.9 | Conclu   | sions                                           |  |

| Add | litional | Examples of TPIE Implementations 119            |  |

| 7.1 |          | Hull                                            |  |

|     |          |                                                 |  |

| 7.2 | 121      |                                                 |  |

| 7.3 | Conclu   | sions                                           |  |

7

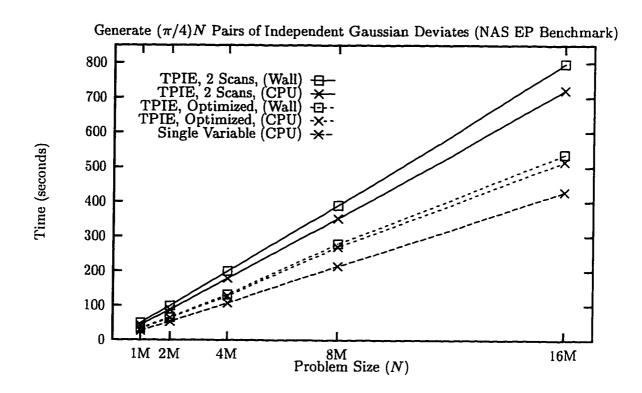

| 8  | TP    | TPIE Prototype Performance                        |     |  |  |

|----|-------|---------------------------------------------------|-----|--|--|

|    | 8.1   | 1 Scanning - The NAS EP Benchmark                 |     |  |  |

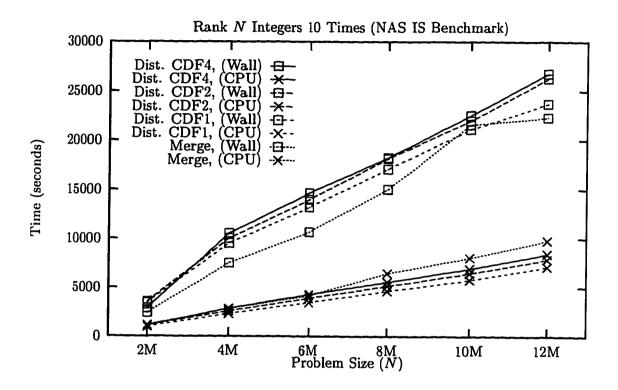

|    | 8.2   | Sorting                                           |     |  |  |

|    | 8.3   | 3 Sparse Matrix Benchmarks                        |     |  |  |

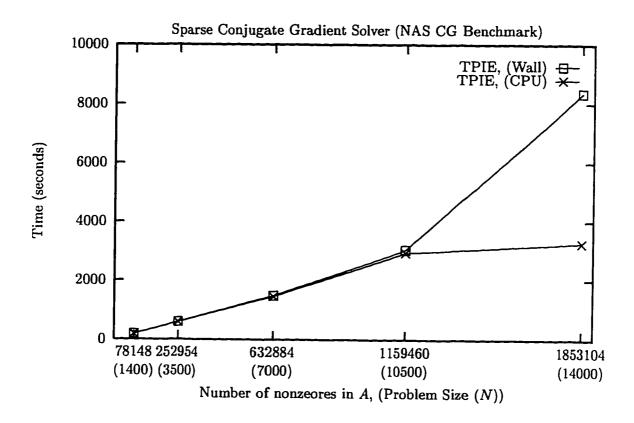

|    |       | 8.3.1 The NAS CG Benchmark                        | 144 |  |  |

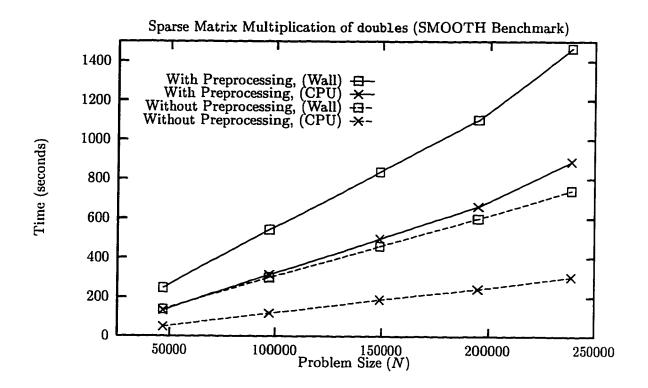

|    |       | 8.3.2 The SMOOTH Benchmark                        | 147 |  |  |

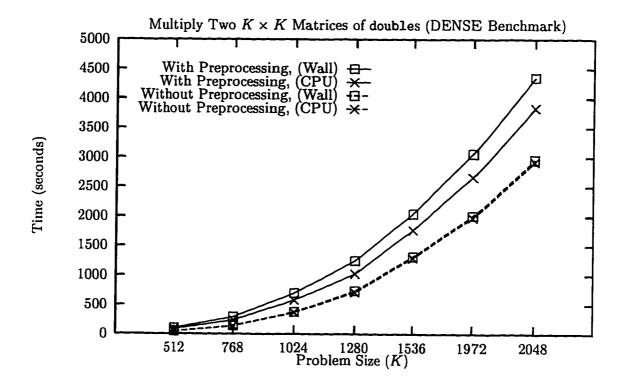

|    | 8.4   | Dense Matrix Benchmark                            | 148 |  |  |

|    | 8.5   | Conclusions                                       | 149 |  |  |

| 9  | Cor   | Conclusions 150                                   |     |  |  |

|    | 9.1   | Algorithm Design and Analysis                     | 150 |  |  |

|    | 9.2   | TPIE: A Framework-Oriented I/O System             | 151 |  |  |

|    | 9.3   | Experimental Analysis of I/O-Efficient Algorithms | 151 |  |  |

|    | 9.4   | Extending Our Work in I/O-Efficient Computation   | 152 |  |  |

|    | 9.5   | Final Thoughts                                    | 153 |  |  |

| Bi | bliog | graphy                                            | 154 |  |  |

# Part I

# **Fundamentals**

## Chapter 1

## Introduction

The subject of this thesis is I/O-efficient computation. Thus, it is only natural that we should begin with some definitions that make it clear exactly what we mean by I/O and I/O-efficient computation. I/O, which stands for Input/Output, is the process of moving data between the main memory of a computer and external memory devices, such as a magnetic disks. Some researchers also use the term to describe communication with other computers through a network, but that definition will not be used herein.

I/O-efficient computation is computation designed to make the most effective use of I/O resources. This is extremely important in large scale applications, because I/O devices are orders of magnitude slower than processors and main memories, and thus I/O often represents a very significant bottleneck in overall program efficiency.

I/O-efficiency is accomplished in two ways: first, by minimizing the amount of data that is moved back and forth across the I/O interface; and second, by moving that data as quickly as possible, with minimal disruption of other resources in the machine, such as the CPU.

#### 1.1 Hierarchical Memory

Hierarchical memory models generalize the Random Access Machine (RAM)<sup>1</sup> model of computation by assigning different costs to accessing different data items depending on their location. In a hierarchical memory system, the time required to access a datum depends on its location within the memory system. Typically, the larger the address, the longer it takes to access data from that address. Hierarchical memory systems are an integral part of virtually all digital computer systems; they always have been, and barring a radical change in our understanding of the laws of physics, they always will be. In 1946, at the dawn of the era of electronic digital computation, Burks, Goldstine and von Neuman wrote,

Ideally, one would desire an indefinitely large memory capacity such that any particular ... word would be immediately available... [however] We are ... forced to recognize the possibility of constructing a hierarchy of memories, each of which has greater capacity that the preceding, but which is less quickly accessible. [BGvN89]

Almost 50 years later, today's workstations and high-performance personal computer systems employ memory hierarchies that begin with tens to hundreds of registers in a physical register file, continue through one or more levels of cache memory to tens or hundreds of megabytes of DRAM main memory and finally move on to several gigabytes of disk space.

Despite the fact that hierarchical memory systems were postulated very early and are ubiquitous today, the majority of programmers still do their work under the assumption that they have a RAM in which all data is accessible with equal cost. There are good reasons for this. RAMs are easy to program, and are the model assumed by most programming languages.

<sup>&</sup>lt;sup>1</sup>Readers unfamiliar with the RAM model of computation are referred a standard algorithms text, such as [CLR90] or [AHU74].

Additionally, computer architects, compiler designers, and operating system designers have all contributed mechanisms that provide the illusion of a RAM to application programmers. At the architectural level, cache management policies implemented in hardware heuristicly determine which data is in the cache at a given time. Compilers solve the register allocation problem to map data to architectural registers which are in turn mapped to physical registers by a hardware register renaming scheme. Operating systems implement paged virtual memory, in which pages of data that are considered unlikely to be needed in the near future are moved to disks to make room for pages that are needed immediately (demand paging) or thought likely to be needed soon (prefetching).

A natural question to ask given the prejudice towards simulating the RAM model at a level beyond the reach of the application programmer is whether or not doing so is appropriate for all applications. The answer is that it is not. There are a number of important classes of programs whose performance suffer if the actual behavior of the memory hierarchy is not taken into account. Poor performance occurs because these applications do not exhibit the locality of reference that RAM simulations require. One example is database systems, which must have the ability to implement their own prefetching and page replacement algorithms instead of relying on the general purpose algorithms provided by most operating systems. Another example is scientific computation, where an unfortuitous combination of array sizes and cache sizes can result in severe performance problems. Scientific computation is discussed in Chapter 5. Additional examples are combinatorial problems on large data sets, which are discussed in Chapter 4.

Rather than attempt the Herculean task of efficiently implementing all possible classes of applications at all levels of the memory hierarchy, our work focuses on a moderately sized set of problems and a specific level of the hierarchy. In particular, we are interested in I/O-efficient combinatorial and scientific computations. These classes

of problems were chosen because they occur widely in large-scale applications programs that deal with data sets are too large to fit in main memory.

We have chosen I/O-efficient computation as the subject of our research for three reasons. First and foremost, there are a large number of applications that depend of I/O-efficient computation. These applications include large scale sorting; geometric computing; geographic information systems; relational and object-oriented databases, statistics; graph theoretic computation; and scientific computation. Second, we believe that despite the trend towards larger and larger main memories, secondary storage devices, whether they be magnetic or optical, will continue to play an important role in computer systems. This will happen not only because certain applications, such as multimedia, demand so much storage space, but also because secondary storage will continue to be more cost effective than solid state technologies. Finally, I/O systems have unique features that make their efficient use particularly challenging. Foremost among these is the use of block transfer to amortize seek latency over large amounts of data. Block transfer forces us to devise algorithms that exhibit a high degree of spatial locality.

## 1.2 A Brief History of I/O-efficient Computation

The earliest use of what could reasonably be called I/O-efficient algorithms actually predates what most of us think of as computer systems. I/O-efficient algorithms were applied to the sorting and tabulation of punched paper cards in the late 19th century. The main concern in the design of sorters and tabulators was reducing the amount of physical movement of cards through various bins and tabulators. A fairly detailed account of the history of their development, including numerous references to early descriptions of the various electro-mechanical devices and algorithmic techniques used can be found in [Knu73].

Paper cards remained in common use for at least eighty more years, well into

the age of electronic computer systems. By the end of World War II, however, it was becoming apparent that magnetic tape devices were both more efficient and more reliable than punched cards for many tasks. Additionally, unlike the early mechanical sorting and tabulating devices, electronic computer systems in the late 1940s and early 1950s had relatively high-speed internal memories. The combination of random access main memory and tape drives gave us systems not entirely unlike those available today. The main differences are that the older systems were physically much larger, much slower, and had significantly smaller storage capacities. One of the most widely studied operations on tapes in the 1950s and 60s was merging, which, at the time was often called collating. Merging is the process of taking several sorted runs and combining them into a single large sorted run. This is accomplished by interleaving the input runs in an appropriate manner. Merging is still an important technique today, and is discussed in a number of contexts in this thesis.

The next important innovations were the development of magnetic drums and, more importantly, magnetic disks. These developments occurred in the 1950s. Unlike tapes, which had to be read and written sequentially, drums and disks have moving heads which can quickly move from track to track over the surface of rotating magnetic media. Thus, the cost of accessing data stored near the end of the device directly after accessing data stored near the beginning of the device is much lower than it would be if the data were stored on a tape.

Although drums have disappeared, magnetic disks are still widely used today. They are, in fact, the device of choice in the vast majority of external memory systems. In order to increase the bandwidth of disk systems, some systems use many disks in parallel. These systems are called Redundant Arrays of Inexpensive Disks (RAID) [Gib92, PGK88, PCGK89], and are becoming increasingly common.

#### 1.3 Related Work

Prior to the work described in this thesis, a substantial amount of research had been done to address problems similar to those we consider. This work can be divided into two camps. On the one hand, theoretical computer scientists have developed models of I/O and algorithms that run on those models. On the other hand, computer systems researchers have designed and implemented a variety of high performance parallel file systems designed to support high-bandwidth, low-latency I/O. In this section, we will briefly review significant work that has been done in both areas in order to establish the context for our work.

#### 1.3.1 Algorithmics

The fundamental difference between the study of I/O-efficient algorithms and the analysis of algorithms in general is that in the latter we are generally concerned with the amount of computation required to solve a given problem, whereas in the former we are primarily concerned with minimizing the costs associated with moving data from one place to another within a computer. In particular, the greatest concern is for the costs associated with moving data from one type of memory to another. As discussed in Section 1.2, a variety of different memory technologies have been used over the years, and algorithms have been developed that are particularly suited to each of their characteristics.

The earliest algorithms specifically designed for disks were probably sorting algorithms based on the merge sorting techniques used for data on tapes. This work was done in the early 1960s, though there is very little formal literature describing it. Knuth [Knu73] mentions an unpublished paper by George Hubbard that was presented in 1963 which examined merges specifically designed for disks.

The earliest widely known work specifically concerned with disks was that of Floyd [Flo72], which considered the problem of permuting data on disks. This work was

the predecessor of numerous more recent papers that have discussed various aspects of permutation on a variety of I/O-models.

Knuth, in his classic work on sorting and searching [Knu73], devoted a significant amount of space to discussion of external sorting algorithms, primarily for tapes, but also for disks.

The I/O-complexity of sorting, fast Fourier transform (FFT), matrix multiplication, and related problems were considered by Aggarwal and Vitter [AV88], who developed a model of sequential I/O on which much of the work in this thesis is based. Vitter and Shriver generalized this model to include multiple independent disks operating in parallel. [VS94a] Both of these models are discussed in detail in Chapter 2.

Analysis of the complexity of computation in more general memory hierarchies has led to the development of a whole series of models, both sequential [ACS87, AACS89, ACF90, ACFS94, VS94b], and parallel [AP94b, ACF93, NV92, NV93c, VS94b].

This work contributed a large number of theoretical results to the field of I/O-efficient computation, but largely ignored issues related to the implementation of algorithms of real systems. These issues have also been studied, although in many cases by different researchers with different motivations and models of computation, as discussed in the next section.

#### 1.3.2 I/O-Efficient Computation Systems

There are two challenges in the design of software systems to support the implementation of I/O-efficient code. First, we must provide programmers with semantics appropriate to the task. This means that programmers should be able both to write functionally correct code and to be able to judge, at least at a high level, how the program will perform based on how it is written. Second, we must provide support, in the form of compilers and/or run-time libraries, that allows the semantic constructs provided to programmers to run efficiently.

In many cases, programmers think more in terms of what has to be computed than where data is physically located. In fact, in programming one typically assumes unit cost for accessing any data item. This notion is encouraged by the structure of many popular programming languages, such as C [KR78], C++[Str86, ES90], FORTRAN [X3J78, ANS90, Ell90], and Pascal [JW75, Wir71].

Unfortunately, for programs to be I/O-efficient, data placement and movement is of great importance, and must be handled either by the programmer or the programming environment. We have identified three classes of systems which solve this problem (or leave it to be solved by the programmer) in different ways. These three classes are array-oriented systems, access-oriented systems, and framework-oriented systems. The distinctions between these classes are almost entirely based on the view of I/O presented to programmers that use them. In the end, solutions to a common problem might result in very similar sets of I/O requests being issued by each of the different types of systems, but the manner in which the programmer wrote the code that led to those requests would typically vary.

#### **Array-Oriented Systems**

An array-oriented system is one in which data stored in external memory is accessed primarily through the specification of element-wise access to arrays of data items of a specific type. Array-oriented systems can be very effective for scientific computations. Such computations typically involve regular strides through arrays of data that are written either as iterative loops or explicitly data-parallel operations.

Array oriented systems are by far the most common of the three types. The main reason they are widely used is that there has been extensive demand from the supercomputer community for high-performance parallel I/O in applications such as computational fluid dynamics, molecular dynamics, and weapon system design and simulation. In these applications, array based languages such as FORTRAN predominate, so it is

not surprising that array-based I/O systems have been proposed to support them.

A classic example of an array-oriented system is PASSION [CBH+94], which consists of a run-time system and a FORTRAN compiler. PASSION's run-time system is largely devoted to supporting access to regular sections of external memory arrays, such as contiguous sub-arrays and regularly strided subsets of array elements. This makes array-oriented systems particularly well-suited to scientific applications with regular, but non-unit strided, data access patterns.

ViC\* [CC94] is a similar system, but it is based on C\*, a data parallel variant of the C programming language [KR78]. ViC\* generalizes C\*'s data parallel shapes<sup>2</sup> to external memory. Programmers using ViC\* write essentially the same C\* code they might otherwise write, except that they mark a certain subset of shapes with the keyword outofcore to indicate that they reside in external memory. A specially constructed compiler translates references to these shapes into a combination of internal computation and calls to library functions that perform the I/O required to access the shape.

Panda [SW94] is another array-oriented system, but it also supports some semantics of access-oriented systems, as discussed below.

The weakness of array-oriented systems is that they are ill-suited to irregular or combinatorial computations. Their weakness in this area is not surprising, since scientific and combinatorial algorithms, whether in the I/O-efficient domain or in the RAM model, demand very different semantics from the systems on which they are implemented. One would not expect most programmers to choose FORTRAN as the language for solving geometric problems; nor should one expect to see them choose an array-oriented system to solve those problems in an I/O-efficient manner.

<sup>&</sup>lt;sup>2</sup>For readers not familiar with C\*, it is sufficient to simply think of shapes as arrays of arbitrary dimension that can have their elements operated on in a data-parallel manner.

#### **Access-Oriented Systems**

An access-oriented system is one which provides language constructs and/or library functions that explicitly move data between main memory and external memory. In some cases this data may be strongly typed, as in array-oriented systems, but in general this need not be the case. Elements of access-orientation must clearly be present at lower levels of array-oriented systems (typically in run-time libraries) in order to move data to and from external memory; the distinction between the array-oriented systems and access-oriented systems lies in the degree to which explicit I/O functionality is exposed to the programmer.

One of the simplest and most familiar access-oriented systems is the UNIX file system. In UNIX, one performs I/O by making a system call specifying a buffer of data and its length. Data is then transferred between the buffer in main memory and a disk or other external device.

In general, programmers writing I/O-efficient applications can benefit from higher-level I/O semantics than are provided by a simple typeless access-oriented approach such as the UNIX I/O interface. As will become apparent in Chapters 4 and 5, there are certain classes of I/O operations that are prevalent in I/O-efficient algorithms. For example, one often wishes to load the entire contents of main memory with data from a disk, or to read or write a sequence of data across several disks. A system that provides this level of functionality frees programmers from having to provide it for themselves. An example of a system of this type is the Whiptail file system [SW95, SWC+95].

The Panda [SW94] system resembles an array-oriented system, since external memory data is stored in arrays, but it is actually more of an access-oriented system, since I/O is performed as a result of specific invocations of I/O routines by the programmer, rather than implicitly by I/O code inserted by a compiler.

The MPI-IO initiative [CFH+95], which seeks to integrate I/O into the MPI parallel programming environment [GLS94] is another example of an access-oriented system.

Appropriately designed access-oriented systems can support the efficient implementation of many I/O-efficient combinatorial algorithms, eliminating one of the weaknesses of array-oriented systems. They do not, however, solve all the problems associated with the implementation of such algorithms. In particular, it is still up to the programmer to manage main-memory resources and explicitly perform all I/O.

#### Framework-Oriented Systems

The final type of system is a framework-oriented system. Framework-oriented systems can be seen as an extension of access-oriented systems which allow the programmer to specify computation that is to take place as an integral part of a particular data access.

The driving notion behind a framework-oriented system is that there are a relatively small number of structural paradigms that are used over and over again in different I/O-efficient algorithms. By a structural paradigm we mean a general method of structuring I/O. For example, many I/O-efficient algorithms read streams of data from external memory and distribute the input data items into a number of output streams. Within this framework, however, different algorithms may use radically different decision-making processes to determine which specific data items go into which output streams. Similarly, the number of output streams may vary significantly depending on the hardware resources available to the running program. Nevertheless, the distribution paradigm is common to all of the algorithms and systems they run on.

Rather than requiring programmers to reconstruct the distribution paradigm for each algorithm, a framework-oriented system provides the paradigm at a high level and leaves programmers with only the task of filling in the functional details. An additional benefit of the framework-oriented approach is that the use of proven paradigms, rather than ad-hoc approaches to solving problems, is encouraged.

TPIE, which is discussed at length in Chapters 6-8 of this thesis, is the first known example of a framework-oriented system.

#### 1.4 Contributions of this Thesis

The goal of this thesis is to demonstrate that a wide variety of scientific and combinatorial problems are amenable to I/O-efficient solutions. This is done through contributions to both the theory and practice of I/O-efficient computation. In particular, this thesis

1. Devises new I/O-efficient algorithms for a variety of combinatorial and scientific problems, and analyzes and improves a number of existing algorithms;

and

2. Presents the design, implementation, and application of TPIE, a Transparent Parallel I/O Environment.

On the algorithmics front, the contributions of this thesis include the development of a number of new algorithmic techniques and the detailed analysis and comparison of several existing algorithms. The algorithmic techniques we developed include

- Distribution sweeping (Section 4.1.1), which produces I/O-efficient algorithms for many problems that are solved by plane sweeping in main memory.

- Batch Filtering (Section 4.1.2), which allows us to answer many geometric queries simultaneously in an I/O-efficient manner.

- An I/O-efficient three-dimensional convex hull algorithm (Section 4.1.3).

- A PRAM simulation technique which is optimal for geometrically decreasing computations (Section 4.2.1).

- New analysis of sorting algorithms (Section 3.2) and dense matrix multiplication (Section 5.2).

- New algorithms for both sparse and dense matrix multiplication (Sections 5.1 and 5.2).

On the implementation side, our contribution is the development of the concept of a framework-oriented system and the design and implementation of the first prototype of such a system. Specifically, our work includes

- The categorization of existing and potential new I/O-efficient computation systems (Section 1.3.2).

- The design and development of TPIE (Chapter 6).

- The implementation of a number of algorithms and benchmark applications in TPIE.

- The analysis of TPIE performance.

We begin our discussion in Chapter 2 by presenting a series of formal mathematical models of I/O-efficient computation. In Chapter 3, we compare striped and independent disk algorithms for sorting and evaluate the conditions under which one or the other are superior. In Chapter 4, we develop a number of new techniques for the I/O-efficient solution of combinatorial problems such as geometric and graph-theoretic problems. These techniques include distribution sweeping (Section 4.1.1), batch filtering (Section 4.1.2), and I/O-efficient simulation of PRAM algorithms (Section 4.2.1). In Chapter 5, we consider I/O-efficient algorithms for scientific computations. In Section 5.1 we develop an I/O-efficient algorithm for multiplying sparse matrices by vectors. In Section 5.2, we compare two algorithms for dense matrix multiplication. We demonstrate that although they are both optimal to within a constant factor, one has a significantly smaller constant factor on its leading term than the other.

Turning from algorithms to implementation, we introduce TPIE in Chapter 6. A number of algorithms have been implemented using TPIE. Some of these are discussed in detail in Chapter 7. We have gathered performance results on a number of benchmarks implemented using TPIE. These are discussed in Chapter 8. In Chapter 9, we

conclude by reassessing our contributions to the theory and practice of I/O-efficient computing and discuss research directions we feel are worth pursuing in the future.

## Chapter 2

## Models and Mathematical

## **Preliminaries**

This chapter introduces the models of computation that will be considered in this thesis. We begin by considering the performance of disks relative to that of solid-state random-access memory. We then examine two models of computation designed to take the behavior of disks into account. The first model is the I/O model of computation, as formalized in [AV88]. The second model is the parallel disk model of Vitter and Shriver [VS94a].

After introducing these models, we discuss and analyze some important algorithmic building blocks designed to enable the development of I/O-efficient algorithms. Algorithms based on these techniques are discussed in Chapters 3, 4, and 5.

## 2.1 Modeling the Behavior of Disks

Compared to random access main memory, disks are extremely slow devices. At the time of this writing, random access dynamic RAM is is widely available with 60ns access time. On the other hand, disks have access times in the 9ms range—approximately 15,000 times slower. We expect that this gap will not only persist, but widen in

coming years. If we compare disks to the caches that feed the execution cores of modern microprocessors, the gap is even wider. Cycle times of 5ns are not uncommon today, and 2-3ns cycle time machines are on the near horizon. Superscalar processors [Joh91] push the gap between disk and processor performance even further, by executing multiple instructions in a single clock cycle.

In recent years, CPU throughput has been increasing at an annual rate of 40–60%, whereas disk access times have only been improving at an annual rate of 7–10% [RW94]. What this tells us is that for applications that require access to very large data sets, there is likely to be a very significant bottleneck in the I/O interface between main memory and the disk. If this bottleneck is not adequately dealt with, then the efforts and expense devoted to CPU and RAM development will be of no use to these applications. The CPU and RAM will simply not be able to be kept supplied with data to work on.

Although disks have high access times, they have reasonable peak bandwidth for sequential accesses. For example, the Barracuda family of disks from Seagate, which includes drives with capacities of 4 and 9.1 gigabytes, have average seek times of 8 to 9.5ms, and internal transfer rates of 47.5 to 120 Mbits per second (5.1 to 15 Mbytes/sec.). Hewlett Packard's SureStore Hard Drive 2000LP offers similar performance, with a transfer rate of 45.7-64 Mbits/sec., and a 9.5ms average seek time. Other manufacturers offer drives with similar performance. By using several disk drives in parallel, we can increase the overall disk bandwidth linearly, without access time penalty. For example, eight of the Hewlett Packard disks in parallel wold provide aggregate bandwidth of 366-512 Mbits/sec.

Data on disks is almost always organized into blocks, which are sequential regions of the disk that are always read or written as entire units. By dealing with large blocks, the latency associated with a single disk access can be amortized over all the data read

<sup>&</sup>lt;sup>1</sup>This is by no means an exhaustive list of models and manufacturers. The performance figures quoted here come from the world wide web pages of the manufacturers mentioned.

or written in the disk access. Of course, an overall computation will only be efficient if most or all of the data in the block is of use in solving the problem at hand. This locality requirement is probably the single largest motivating factor in the design of I/O-efficient algorithms.

In the models of computation that follow, we will consider the cost of accessing any single block on a disk to be constant. It is possible to construct more detailed models of disk drive behavior, as done in [RW94], but such models are necessarily tied to specific makes and models of disk drives, and do not allow us to reason about the I/O complexity of algorithms on a more general level. Our philosophy in modeling and designing I/O-efficient computation is that by treating each I/O operation as if it had unit cost, we will construct algorithms that will minimize the number of I/O operations, and thus operate efficiently on a variety of different types of disks. This is essentially analogous to assuming that all operations on a random access machine are of unit cost despite the fact that they certainly aren't on real machines.

### 2.2 The I/O Model of Computation

The I/O model of computation was introduced by Aggarwal and Vitter [AV88]. It formalized and generalized the models of I/O used by a number of earlier researchers [Knu73].

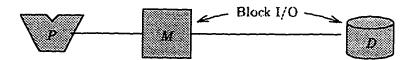

In the I/O model, we have a single CPU and uniform cost random access memory, just as in the RAM model, but we also have a single disk. The CPU cannot perform computation directly on data residing on the disk, but instead must move it into main memory first. Because the main memory has a limited capacity, it is also often necessary to move intermediate results of a computation from the main memory back out to the disk in order to free up space for more data to be read in from the disk. The I/O model is illustrated in Figure 2.1.

In the I/O model, the capacity of the main memory is M, which is assumed to be in

Figure 2.1: The I/O model of computation. In this model, there is a single processor P connected directly to a random-access main memory of fixed capacity M. Beyond this main memory is a disk, whose capacity is unbounded. Data on the disk cannot be directly accessed by the processor. Instead, it must first be transferred into the main memory. Data that that been processed or generated into main memory by the processor must be transferred to the disk to make room for new data.

All data transfer between the main memory and the disk is done in large contiguous blocks. Each block consists of B data items. The I/O complexity of a task in this model is measured in terms of the number of block transfer operations required to complete the task.

units of some basic object over which computation is performed. Such objects consist of a constant number of machine words. For example, if we are dealing with a graph represented as a set of edges, then M would be the number of edges that can fit in main memory. If each edge took 32 bytes to represent, and a total of 16 megabytes of memory was available, then M would be  $2^{19}$ .

The capacity of the single disk attached to the system is assumed to be unbounded, so that all intermediate and final results that it might need to store can be handled. The surface of the disk is divided into a series of blocks, each of which has a capacity B. The blocks are numbered sequentially, starting with 0. Any input to a particular algorithm is assumed to be stored sequentially at the beginning of the disk. In other words, a problem consisting of N input objects will be stored on the first  $\lceil N/B \rceil$  blocks of the disk.

Data is transferred to and from the disk one block at a time. Each block transfer is counted as a unit of I/O complexity. In between I/O operations (I/Os for short) the CPU is permitted to perform an arbitrary amount of computation.

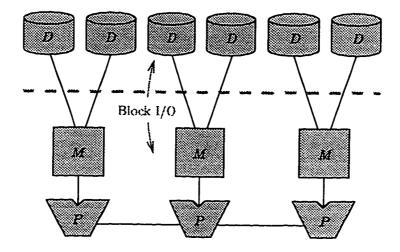

Figure 2.2: The parallel disk model of computation. This model generalizes the I/O model shown in Figure 2.1 by replacing the single disk with several disks in parallel. There may also be several processors in parallel, as shown here, although this is not strictly required by the model. If there are multiple processors, then the main memory may be distributed among them, as shown here, or shared. The reason the details of the processor and memory architecture are not fully specified in the model is that its goal is primarily to model the amount of I/O required in solving a problem (that is the number of I/O operations that bring data across the heavy dotted line in the illustration), rather than the amount or structure of the internal computation done in conjunction with the I/O.

In a single I/O operation, the parallel disk model can transfer a block of data to or from each and every disk in parallel. Thus, much greater aggregate disk bandwidth can be achieved in this model than in the single-disk I/O model.

#### 2.3 The Parallel Disk Model

The I/O model of computation can be generalized to include parallel processors and parallel disks. The former essentially turns the processors and main memory into a PRAM [FW78], while the latter introduces a number of interesting twists into the I/O picture. An example of this generalization is shown in Figure 2.2.

In the parallel disk model, we can access one block on each of the D disks in the system in a single I/O operation. We restrict the total main memory capacity M to be strictly greater than DB, in order to ensure that there is adequate main memory

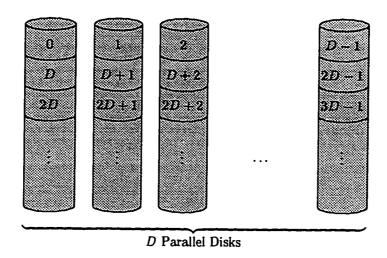

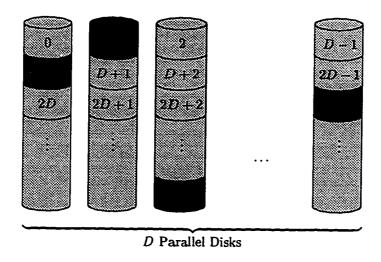

Figure 2.3: Parallel disk block ordering. In this illustration, the blocks on each of the D disks are indicated by slices of the disks. The block numbers are assigned by beginning with the first block of the first disk, in the upper left corner of the illustration. The next block is the first block on the second disk. Numbering continues until the first block on each disk has been assigned a number, at which point we begin with the second block of the first disk and proceed through the second blocks of all the other disks. This process then continues through all logical block positions.

to support such I/O operations.

On a single disk there is an implied logical ordering of blocks based on their physical location on the disk. When several disks are used in parallel, we need a way of generalizing this ordering. The ordering used in the parallel disk model is illustrated in Figure 2.3. We order blocks by their physical position on a single disk, and order blocks at the same physical location on different disks by a set of logical disk numbers assigned to the disks.

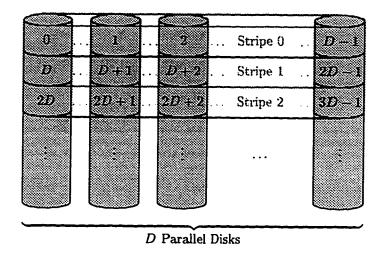

There are two common approaches to performing I/O on parallel disk systems. The first method, called disk striping [Kim86, LKB87, SGM86], is illustrated in Figure 2.4. Disk striping reads or writes a block of data in the same logical position on each of the D disks in a single I/O operation. For example, we might read logical block 17 from every disk, or write to logical block 3 of each disk. This technique is called striping

Figure 2.4: Parallel disk striping. In this approach to managing data on parallel disks, an I/O operation must consist of either one read or one write to each of the D disks. Furthermore, the blocks referenced on each of the disks must be in the same logical position on each disk. This is illustrated with the highlighted "stripes" shown above, which we can number logically based on the logical numbers of the blocks that make them up. These stripes look very much like large blocks of size B' = DB data items which must read as a group. The net effect is that the D parallel disks essentially simulate a single larger disk with block size B'.

because it "stripes" data objects across the disks as if they were a single large disk with blocks of size B' = DB.

The second method of accessing data on parallel disks is called independent access. As its name implies, independent access allows the machine to read and/or write blocks in different positions on each of the D disks in a single I/O operation. This is illustrated in Figure 2.5.

Clearly the independent disk model is at least as powerful as the striped model, since it can trivially mimic the behavior of a striped disk system. It can be shown theoretically that this model admits algorithms that, in the limit as problem sizes grow extremely large, require less I/O than any that can be implemented on striped disk systems of similar size. However, it is also the case that such algorithms tend to be less

Figure 2.5: Independent access to parallel disks. In a single I/O operation one block can be read from or written to each disk. Unlike striped access, the blocks being accessed on different disks need not come from the same logical location. For example, a single I/O operation might read each of the shaded blocks in this illustration.

efficient than striped disk algorithms on systems of moderate size. The relationship between these two models in this context is discussed at greater length in Section 3.3.

## 2.4 Paradigms of I/O-Efficient Computation

There are a number of paradigms that are repeatedly in I/O efficient computations. Three of the most important are scanning, distribution, and merging, which are discussed in the following three sections.

#### 2.4.1 Scanning

Scanning is the process of examining each element of a collection of objects stored in external memory, possibly performing some transformation on each, and then writing them back out to external memory.

Scanning is done in an I/O-efficient manner through the use of buffering. Buffering

is done by allocating a region of main memory, called a buffer, of size B. A block of data from the disk is read into the buffer, and then the contents of the buffer are examined sequentially. Once every item in the buffer has been examined, the next block is read into the buffer and its contents are examined sequentially. When all blocks of data have been examined, the process is complete.

If a scan wishes not only to examine data, but to transform it in some way, the transformed data items are placed one-by-one into an output buffer of size B which resides in main memory. Once this output buffer is full, it is written out to a disk in a single I/O operation, and then the main memory buffer space can be re-used to buffer more output.

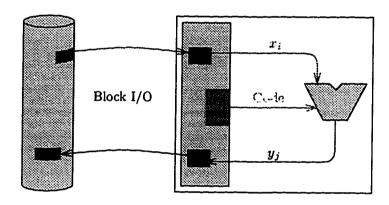

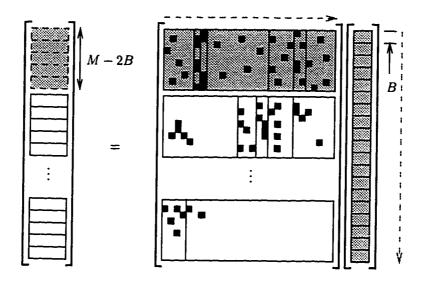

An example of a scan is shown in Figure 2.6. Data is read from the disk at the left of the figure one block at a time into the main memory. The input data items  $x_i$  are read from the buffer one at a time and the CPU applies some transformation to them, producing output data items  $y_j$ . These items are written into an output buffer of size B. When this output buffer becomes full, it is written out to the disk in a single I/O operation.

It was mentioned above that a scan might only read data, and not produce any output. The reverse can also be true. A scan can write data without reading any, if the program that is performing the scan is one that is written so as to generate streams of output data dependent only on its changing internal state.

We can summarize the I/O-complexity of scanning with the following simple lemma, whose proof is apparent from the description of scanning given above.

Lemma 2.1 A scan operation that reads  $N_i$  items and writes  $N_o$  items can be performed using

$$O\left(\frac{N_i + N_o}{B}\right)$$

I/O operations.

Figure 2.6: Scanning a collection of data items using input and output buffers. At the top of the figure, a block of B input items is read from the disk into main memory. Once this block is in main memory, the individual items  $x_i$  that it contains are fed sequentially through some function computed by the CPU. An application of the function may produce an output item  $y_j$ . If is does,  $y_j$  is placed in an output buffer of size B in main memory.

Once all the items from the input buffer have been exhausted, a new block of input is read from the disk into the main memory buffer in a single I/O operation. If the output buffer holding the  $y_j$  gets full, then its contents are written out to a disk in a single I/O operation and it is emptied to allow more output items to be generated.

In the parallel disk model, Lemma 2.1 generalizes as follows:

Lemma 2.2 In the parallel disk model, a scan operation that reads  $N_i$  items and writes  $N_o$  items can be performed using

$$O\left(\frac{N_i + N_o}{DB}\right)$$

I/O operations.

**Proof:** Instead of using buffers of size B, we use buffers of size DB and read and write stripes of data from or to all the disks in a single I/O operation.  $\Box$

The low I/O complexity of scanning is by far the most important reason it is widely used. The most important aspect of this complexity is the presence of the B (or DB) in the denominator, indicating that we are making full use of the potential of blocking.

The I/O complexity of scanning is the external memory analog of linear time (O(N)) in the RAM model, and we will often refer to it as a linear amount of I/O or linear I/O complexity. The difference between linear time in a RAM and a linear amount of I/O is that in external memory data must be processed with a significant degree of locality to compensate for the effects of blocking, whereas in a RAM, it can be processed in any order. This leads to an important distinction between linear and non-linear I/O complexity when it comes to algorithms that must perform permutations. This distinction is discussed in Section 3.1.

Scanning is used extensively in the algorithms discussed in Chapters 4 and 5. It is also discussed at length in Chapter 6, where techniques for simplifying its incorporation into I/O-efficient programs are discussed.

### 2.4.2 Distribution and Merging

Distribution and merging are both generalizations of scanning. Instead of reading or writing individual streams of inputs and outputs, distribution reads a single stream

of input and writes objects from that stream into many output streams. Merging is similar, except that it reads many input streams and combines them into a single output stream.

The number of input or output streams merged or distributed is limited by the availability of main memory. Given a main memory of size M, we can buffer M/B inputs or outputs in the single disk model.

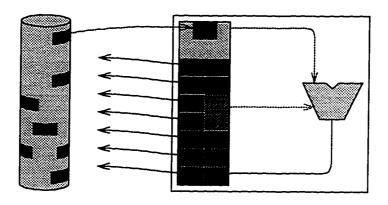

Distribution allows us to handle many problems using divide-and-conquer approaches. We distribute the input into subproblems, and then recursively solve those. When the problem instances become smaller than M, we solve them in main memory. Merging, being the opposite of distribution, allows us to construct solutions for larger problems from the solutions to smaller subproblems. Distribution is illustrated in Figure 2.7.

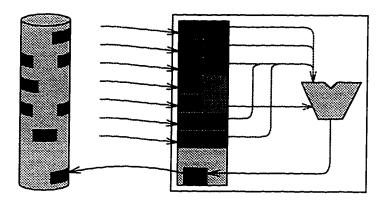

Merging is illustrated in Figure 2.8. It is essentially the same as distribution, except that data moves in the other direction, from many input buffers to a single output buffer.

The I/O complexity of merging M/B input streams, each of length  $N_{in}$ , into one output stream of length  $N_{in}M/B$  is  $O(N_{in}M/B^2)$ , since all reads and writes are fully blocked. If we start with inputs of size M, then after one merge we would have intermediate streams of length  $M^2/B$ . If we merged M/B of these intermediate streams, we would end up with streams of length  $M^3/B^2$ . We could repeat this process over and over again, and given enough original inputs, generate outputs of enormous size.

In many applications, we have N items originally divided into sets of size O(M), which are small enough to be read once, processed entirely in main memory, and then written back out to disk. In order to merge these sets back into one set of size N using the procedure just outlined, the number of I/Os needed would be

$$\frac{N}{B}\log_{M/B}\frac{N}{M/B} = O\left(\frac{N}{B}\frac{\log N}{\log(M/B)}\right).$$

Figure 2.7: I/O-efficient distribution of data. Distribution is very similar to scanning, except that there is a single input buffer and many output buffers. In most cases, the number of output buffers is limited by the amount of main memory available in the machine. The code decides which output buffer each input item should be placed in. As was the case in scanning, the input buffer is refilled when all data has been read from it and the output buffers are written to the disk when they get full. The sequence of blocks written from a particular output buffer is treated as a logical collection of data items that is separate from those data items written from other output buffers, even though they may reside on the same disk. Mechanisms for implementing this logical relationship between blocks are discussed in Section 2.4.3. Once all data has been distributed, each of the output collections of data can be used as input to another distribution or scan.

Figure 2.8: I/O-efficient merging of data. Merging is, in a sense, distribution turned around. We have as many input buffers as our main memory capacity allows, and a single output buffer. The code that supervises the merge must decide how to interleave the input items into the output.

This quantity is essentially the analog of  $O(N \log N)$  time in the RAM model of computation. We can sort in this bound, using merging, and many other problems that have  $O(N \log N)$  time algorithms in the RAM model can also be solved within this I/O bound. Many algorithms that use distribution also operate in this I/O bound.

#### 2.4.3 Block Linking and Meta-data

In our descriptions of scanning, distribution, and merging, we assumed that there was no cost associated with reading the next block from a stream other than the single I/O operation required to read the block itself. If data in blocks are arranged in physical position order on the disk, this assumption is valid. Unfortunately, this arrangement limits us to one logical stream of data per disk drive. In practice this is unreasonable and must be dealt with by providing some mechanism to group blocks from different parts of the disk into ordered logical collections.

The problem of ordering blocks can be handled in one of two ways. The most

common way is to rely on the same file system mechanisms that are designed to link blocks into a logical file, namely file system meta-data. Technically, since file system meta-data is resides on disk, its manipulation requires I/O and main memory buffer space in addition to that actually used for data. This overhead, however, is generally quite small. Indeed, since most file meta-data consists of pointers to blocks of data or additional file meta-data, the overall size of meta-data for a large file is on the order of B times smaller than the file itself.

The second way of linking blocks is by reserving a few bytes at the beginning or end of each block for a pointer to the next block in a collection of blocks. This eliminates extra I/O for meta-data, but it also reduces the effective size of each block slightly.

Assuming data items and pointers are of the same size, the tradeoff is that a file of size N with meta-data takes roughly  $N/B + N/B^2$  blocks, while one using pointers within blocks takes

$$\frac{N}{B-1} = \frac{N}{B} \left( \frac{1}{1-1/B} \right)$$

$$= \frac{N}{B} \left( \sum_{i \ge 0} \frac{1}{B^i} \right)$$

$$= \sum_{i \ge 0} \frac{N}{B^i}$$

blocks. The space overhead is very similar to that of meta-data, since in both cases the leading term of the overhead required on top of the N/B blocks needed just to store data is  $N/B^2$ . If data items are larger than pointers and blocks have room for exactly an integral number of data items of the same size, then the analysis is essentially the same. The only difference is that the overhead for meta-data will be a constant factor smaller that that for pointers. In the case where data items are large, but there is extra space at the end of each block because a non-integral number of items fit in each block, then it may be possible to integrate pointers with no overhead whatsoever. In any case, however, the overhead is quite small.

The more important difference between the use of meta-data and pointers is that the pointer method requires that code be written to explicitly manage and follow pointers when locating blocks of data. Care must be taken not to overwrite pointers with data, since they reside in the same blocks.

In most of this thesis, we will not directly concern ourselves with which of the two methods is used. Instead, we will simply refer to collections or streams of data on disk and assume that an appropriate mechanism is being used.

### Chapter 3

## Permutation and Sorting

Permutation and sorting are among the most widely studied types of I/O-efficient algorithms. Although they are not the primary focus of this thesis, they are important building blocks for many of the algorithms that will be discussed in Part II. Additionally, a thorough understanding of their subtleties is required by anyone wishing to implement I/O-efficient computations in practice.

In this chapter, we will discuss lower bounds on permutation problems and analyze the relationship between two classes of algorithms for parallel disks.

# 3.1 Lower Bounds: Linear Complexity vs. Permutation Complexity

In order to verify the optimality of various algorithms we might wish to construct for the models outlined in Chapter 2, it is important that we understand the fundamental lower bounds on the amount of I/O required to solve a particular problem. We will initially explore these lower bounds for the single disk I/O model, and then extend them for the parallel disk model.

The first lower bound we will consider is for the fundamental problem of reading in

an input of N data objects, so that each data object is, at some point, in main memory. This problems is sometimes referred to as the "touch problem" because it requires that every input object be touched at least once [ACF90, NV90, VS94b]. The trivial lower bound on this problem is given by the following lemma:

Lemma 3.1 In the I/O model of computation, solving the touch problem requires at least [N/B] I/O operations.

**Proof:** Suppose that less than  $\lceil N/B \rceil$  blocks are read to solve the touch problem. Then there exists at least one block that is never read, which contains some input objects that are therefore never touched. Thus the touch problem cannot be solved with less than  $\lceil N/B \rceil$  I/Os.  $\square$

This lower bound can be achieved by scanning, as discussed in Section 2.4.1. At times we will use the shorthand notation scan(N) instead of N/B, in expressing the I/O complexity of algorithms or portions thereof that use scanning or variations of it. This expression is commonly referred to as linear time in the I/O model.

In order to derive lower bounds for the amount of I/O required to solve problems less trivial than the touch problem, it is often useful to look at the complexity of the problem in terms of the number of permutations that may have to be performed to solve it. In an ordinary RAM, any known permutation of N items can be produced in O(N) time. In an N processor PRAM, it can be done in constant time. In both cases, the work is O(N), which is no more than it would take us to examine all the input. In external memory with blocking, however, it is not generally possible to perform arbitrary permutations in a linear number (O(scan(N))) of I/Os. In the worst case,  $\Theta(perm(N))$  I/Os are required, where

$$perm(N) = \min \left\{ \frac{N}{D}, \frac{N}{DB} \frac{\lg N/B}{\lg M/B} \right\}$$

[AV88, VS94a]. When M is extremely small, the  $\Theta(N/D)$  term may be smaller, but

for values encountered in any real system, the second term is the smaller of the two.

### 3.2 Sorting

Sorting is one of the most widely studied problems in algorithmics. Literally hundreds of papers have been written on the subject in all manner of computational models. We will discuss it here in order to illustrate the differences between the models of computation we introduced Chapter 2. Our emphasis will be on fully analyzing the algorithms, including the constant factors often hidden by big-Oh notation, taking implementation details into account.

First, let us consider the single disk I/O model of computation. In this model, the sorting algorithm of choice for comparison sorting is merge sort.<sup>1</sup> As mentioned in Chapter 1, merge sort was used on tapes, and later adapted for use on disks [Knu73].

In order to slightly simplify our analysis, we will assume that M is an integral multiple of B and that N is an integral multiple of M. If this is not the case, a small amount of memory (< B items) can be left unused, and/or the problem can be padded with a small number of data items.

Merge sort begins by reading the first M input items into main memory, sorting them internally, and writing them back out. The next M items are then processed in the same way. This continues until all input has been processed and we have N/M sorted subfiles. The total amount of I/O required to produce these sorted subfiles is 2N/B.

Next, we merge sets of O(M/B) sorted subfiles together into sorted output files. In order to do this, we allocate a main memory input buffer of O(1) blocks for each subfile and an output buffer for the output file. The data items from a particular input file are read sequentially from that file's input buffer, though the order in which they are

<sup>&</sup>lt;sup>1</sup>Radix sort is often used when the structure of keys permits it, but our concern is with keys that must be compared as indivisible units, and this are not amenable to radix sorting.

read relative to data from other input files is data dependent. When an input buffer is empty, it is refilled by an I/O. An internal memory data structure, such as a heap or other priority queue, is used to manage the merging process, by properly interleaving data from the input files into a sorted output. Assuming N is large, the result of this first set of merges is a set of  $O(NB/M^2)$  sorted subfiles of length  $O(M^2/B)$ .

The results of the first set of merges are then merged together O(M/B) at a time to form larger sorted subfiles of length  $O(M^3/B^2)$ . This merging process continues until we have one large file of length N, which is fully sorted.

If we take a closer look at how merge sorting is normally implemented, we find that in most cases double buffering, which is the use of two blocks of main memory for each input and output buffer, is used. Double buffering allows I/O to be done on one of a buffer's blocks while the CPU is still accessing data in the other, which lowers the overall running time of merge sort by allowing the CPU and I/O system to be active at the same time. With double buffering, there is enough main memory available to merge M/2B-2 inputs into a single output. The additive term -2 is to account for the use of two buffers for the output. Thus, the number of levels of merging required is

$$\left\lceil \log_{\frac{M}{2B}-2} \frac{N}{M} \right\rceil = \left\lceil \frac{\log \frac{N}{M}}{\log \left(\frac{M}{2B}-2\right)} \right\rceil.$$

The total amount of I/O performed at each level of the merge is 2N/B, since every data item is read once and written once. Additionally, there is an initial pass through the data to produce the initial sorted runs, which required 2N/B I/Os. Thus, the total amount of I/O performed is

$$\frac{2N}{B}\left(1+\left\lceil\frac{\log\frac{N}{M}}{\log\left(\frac{M}{2B}-2\right)}\right\rceil\right).$$

If we extend merge sorting to parallel disks using disk striping, then the total

number of I/Os performed in a merge sort is

$$\frac{2N}{DB}\left(1 + \left\lceil \frac{\log\frac{N}{M}}{\log\left(\frac{M}{2DB} - 2\right)} \right\rceil\right). \tag{3.1}$$

Asymptotically, the I/O bound (3.1) is not optimal for sorting on parallel disks. There are a number of optimal sorting algorithms for parallel disks [AP94a, Arg94, BGV97, NV93a, NV93b, VS94a]. Most of these algorithms use distribution, as discussed in Section 2.4.2, but they take special care to ensure that data is evenly distributed among the independent disks. One algorithm, [BGV97] is based on merging. The leading term of the I/O complexities of all of these algorithms is of the form

$$2k\left(\frac{N}{DB}\right)\left(\frac{\log\frac{N}{M}}{\log\frac{M}{2B}}\right) \tag{3.2}$$

for some constant  $k \geq 1$  that depends on the particular algorithm chosen. The distribution sort algorithm works from the top down by computing medians in the data and then distributing the data into buckets based on the median values. The buckets are then recursively sorted and appended to one another to produce the final output. The value of the constant k depends on the complexity of finding the medians, the quality of the medians as partitioning elements, and the evenness of the distribution of the buckets over the D disks.

Although the the denominator in (3.2) is larger than the denominator in (3.1) by an additive term of  $\lg D$ , the leading constant factor in (3.2) is larger than that of (3.1) by a multiplicative factor of k. The value of k for currently known distribution algorithms ranges from approximately 3 to 20. The value of k for the merge sort algorithm of [BGV97] is typically in the range of 1 to 2.

If either k or D is too large, merge sorting using striping may be significantly more efficient than independent disk approaches that are asymptotically optimal. We will examine the exact nature of the relationship between these two approaches and the

number of disks in the next section.

### 3.3 Comparing Independent Disk Sorting and Striped Disk Sorting

Before implementing an external sort on parallel disks, it is essential determine which algorithm is most appropriate to the system on which the the code is to run. To compare striping to independent-disk models, we must examine the circumstances under which the I/O complexity (3.2) for using the disks independently is less than the I/O complexity (3.1) with striping. To simplify our analysis, we will compare the leading terms of (3.2) and (3.1), ignoring the ceiling operators. Doing so, we find that the independent disk model requires fewer I/Os whenever

$$k\left(\frac{2N}{DB}\right)\frac{\lg\frac{N}{M}}{\lg\frac{M}{2B}} < \left(\frac{2N}{DB}\right)\left(\frac{\lg\frac{N}{M}}{\lg\frac{M}{2DB}}\right).$$

Eliminating a common factor of 2N/DB and dividing through by  $\lg \frac{N}{M}$  tells us that this occurs exactly when

$$\frac{k}{\lg \frac{M}{2B}} < \frac{1}{\lg \frac{M}{2DB}}.\tag{3.3}$$

As the number of disks D in our system grows, the right hand side of (3.3) increases, while the left hand side remains the same. Thus, if the inequality holds for some value of D, say  $D^*$ , then it holds for all  $D > D^*$ . For a given algorithm with a fixed constant k, we would like to find out the minimum number of disks  $D^*$  for which (3.3) holds. Making an equality of (3.3) and solving for D gives us

$$\frac{k}{\lg \frac{M}{2B}} = \frac{1}{\lg \frac{M}{2DB}}$$

$$k \lg \frac{M}{2DB} = \lg \frac{M}{2B}$$

$$\left(\frac{M}{2DB}\right)^k = \frac{M}{2B}$$

$$\left(\frac{1}{D}\right)^k = \left(\frac{M}{2B}\right)^{1-k}$$

$$D^k = \left(\frac{M}{2B}\right)^{k-1}$$

$$D = \left(\frac{M}{2B}\right)^{\frac{k-1}{k}}.$$

Thus, D must be at least some root of M/B. The critical issue now becomes the value of k. If k=1, i.e., if we do not need extra I/Os to compute M/2B medians that partition the data evenly and if each resulting bucket is divided evenly among the D disks, it is better to use disks independently. However, if k=4, we need  $D>(M/2B)^{3/4}$  in order for using disks independently to be worthwhile. This is a rather unreasonable number of disks for any realistic system. For example, suppose we are sorting on a machine with 256 megabytes (=  $2^{28}$  bytes) of RAM and disk blocks of 8 kilobytes (=  $2^{13}$  bytes). On this machine, we would need

$$\left(\frac{M}{2B}\right)^{3/4} = \left(2^{28-13}\right)^{3/4} = 2^{45/4} = 1449$$

disks for the independent disk algorithm to do better than striping. On the same system, an algorithm with k = 1.5 could outperform striped merge sort on a much more reasonable 26 disks. It is not clear at this point how close to 1 that k can get. What is clear, however, is that only algorithms for which k is quite small, such as the merge sorting algorithm of [BGV97], can compete with striping on machines of any reasonable size.

Another important aspect of the behavior of I/O-efficient algorithms for sorting

concerns the behavior of the logarithmic factor  $\lceil \lg(N/M)/\lg(M/2DB-1) \rceil$  in (3.1). The logarithmic term represents the number of merge passes in the merge sort, which is always integral, thus necessitating the ceiling notation. The ceiling term increases from one integer to the next when N/M is an exact power of M/(2DB)-1. Thus over very wide ranges of values of N, of the form  $M^i/(2DB-1)^i < N/M \le M^{i+1}/(2DB-1)^{i+1}$  for some integer  $i \ge 1$ , the I/O complexity of sorting remains linear in N. Furthermore, the possibility of i > 3 requires an extremely large value of N if the system in question has anything but the tiniest of main memories or a huge number of disks. As a result, although the I/O complexity of sorting is not, strictly speaking, linear in N, in practice it often appears to be over very wide ranges of N.

Many of the algorithms discussed in Part II of this thesis exhibit behavior similar to that of sorting on striped or independent disks. For this reason, they will be discussed in the context of single disk systems. The extension of these algorithms to parallel disks by striping will not necessarily yield theoretically optimal algorithms, though it will produce algorithms that are very efficient in practice.

# Part II

# Algorithms

### Chapter 4

# Combinatorial Algorithms

Combinatorial algorithms are algorithms for problems on data sets consisting of discrete structures. In this chapter, we concern ourselves with two important classes of combinatorial problems: geometric problems and graph theoretic problems.

### 4.1 Geometric Algorithms

Geometric problems, that is to say problems whose inputs and/or outputs are geometric objects, have been widely studied, and solutions to many are well known [PS85]. These solutions typically assume a RAM model of computation, although significant work has also been done for parallel machines, primarily using the PRAM model [ACG+88, AL93].

In this section, we will examine techniques for developing I/O-efficient geometric algorithms. These algorithms have important applications in a number of domains. For example, design-rule checking on a very large VLSI design may involve looking for intersections among tens or hundreds of millions of rectangles. Another set of examples come from geographic information systems (GIS), which store tremendous amounts of

<sup>&</sup>lt;sup>1</sup>The work presented in this chapter originally appeared in two separate papers: [GTVV93], which was joint work with Michael Goodrich, Jyh-Jong Tsay, and Jeffrey Vitter; and [CGG+95], which was joint work with Yi-Jen Chiang, Michael Goodrich, Eddie Grove, Roberto Tamassia, and Jeffrey Vitter.

inherently geometric data. The particular problems we consider include line segment and rectangle intersection, nearest neighbor queries, and convex hulls in two and three dimensions.

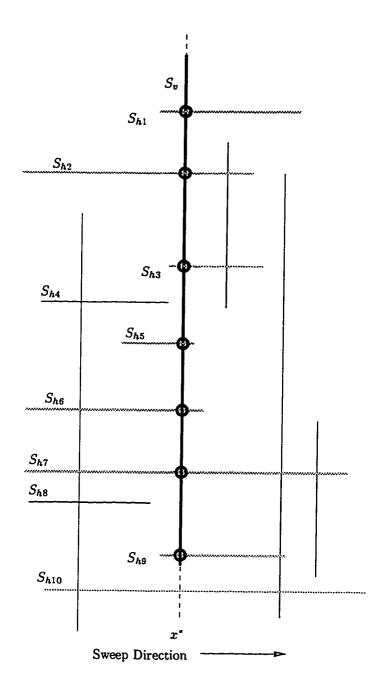

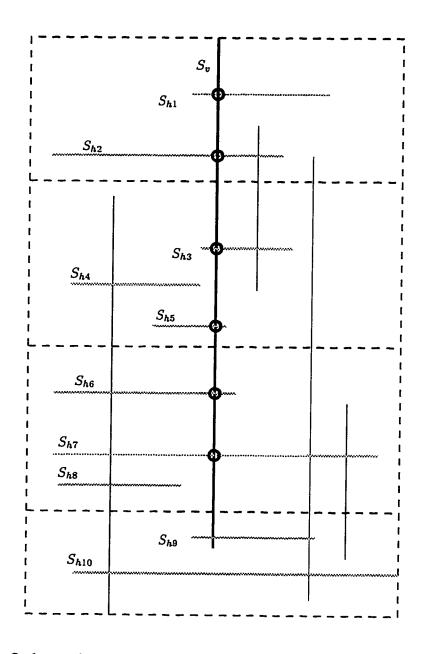

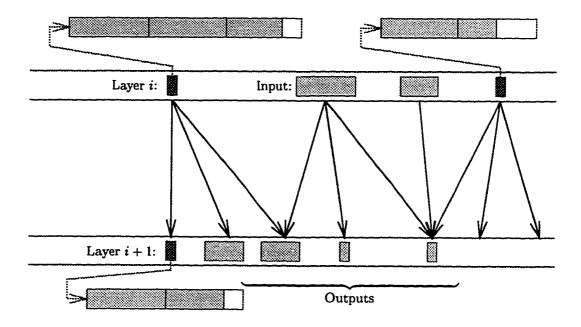

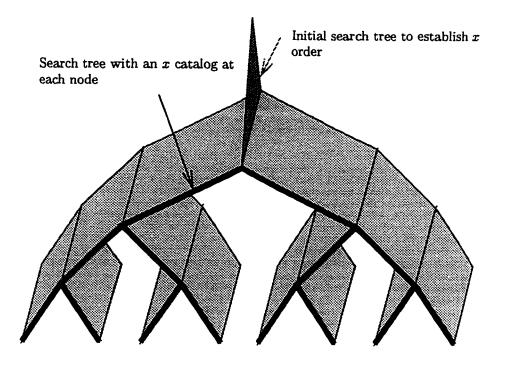

We will discuss geometric algorithms in the context of a single disk model of I/O, though the results can be extended to other models as well. In particular, they can be extended to parallel disk systems through the use of striping, as discussed in Section 2.3. For systems of reasonable size, striping will produce algorithms that are more efficient than the more complicated algorithms required to make optimal use of independent disks.<sup>2</sup> The effect is essentially the same as that seen for sorting in Section 3.3.