# Nanowire Addressing with Randomized-Contact Decoders

Eric Rachlin and John E. Savage Computer Science, Brown University Providence, RI 02912-1910 {eerac,jes}@cs.brown.edu

Abstract—Methods for assembling crossbars from nanowires (NWs) have been designed and implemented. Methods for controlling individual NWs within a crossbar have also been proposed, but implementation remains a challenge. A NW decoder is a device that controls many NWs with a much smaller number of lithographically produced mesoscale wires (MWs). Unlike traditional demultiplexers, all proposed NW decoders are assembled stochastically. In a randomized-contact decoder (RCD) [11], for example, field-effect transistors are randomly created at about half of the NW/MW junctions.

In this paper, we tightly bound the number of MWs required to produce a correctly functioning RCD with high probability. We show that the number of MWs is logarithmic in the number of NWs, even when errors occur. We also analyze the overhead associated with controlling a stochastically assembled decoder. As we explain, lithographically-produced control circuitry must store information regarding which MWs control which NWs. This requires more area than the MWs themselves, but has received little attention elsewhere.

## I. INTRODUCTION

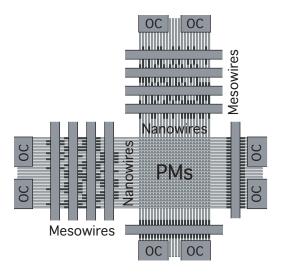

Nanotechnology offers the promise of constructing memories and programmed logic arrays with very high densities [7], [6]. The approach is to form crossbars (see Figure 1) by stamping or imprinting uniform nanowires (NWs) on a chip [3], [2], [14] or by growing differentiated nanowires off chip and then assembling them fluidically on a chip [17], [19]. A crossbar with switchable crosspoints is grown by placing a supramolecular layer between two orthogonal sets of NWs. The molecules in this layer act either as diodes and carry current or they form open circuits [4], [5], [13]. The application of a high positive or negative electric field by the NWs that form a crosspoint drive the molecules into one of these two states. With small modifications, such memories can function as (non-restoring) programmed logic arrays.

To store data at crosspoints requires that NWs in each dimension of a crossbar be addressable. That is, it must be possible to cause one (or a few identical) NWs in each dimension to have a low resistance while the others have high resistance.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. ICCAD'06, November 5-9, 2006, San Jose, CA Copyright 2006 ACM 1-59593-389-1/06/0011...\$5.00

This work was supported in part by NSF Grant CCF-0403674. Presented at ICCAD 2006.

The state of the molecules at a crosspoint defined by the low resistance NWs can then be read or written. Control over NW resistances is achieved through the application of electric fields to NWs using orthogonal lithographically defined mesoscale wires (MWs), as suggested in Figure 1. A small number of MWs can be used to address a large number of NWs.

The device which controls NW resistances is called a **nanowire decoder**. Three types of NW decoder are described in Section II, the "encoded NW decoder," the "mask-based decoder," and the "randomized-contact decoder." NWs are organized into **simple decoders** consisting of a set of NWs (a **contact group**) between a pair of **ohmic contacts (OCs)**. The entire decoder consists of multiple contact groups (a **compound decoder**). Two orthogonal sets of N/w contact groups, each containing w NWs, can be used to form an  $N \times N$  crossbar, as suggested in Figure 1.

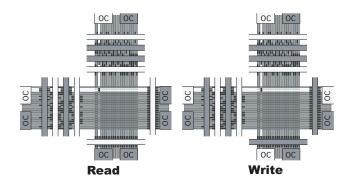

To use the crossbar as a memory, a voltage is applied to a single contact group of NWs along each dimension of the crossbar. Subsets of MWs along each dimension are then used to address NWs within each of the two groups. This operation can either read or write a single bit to the crosspoints of the NWs being addressed (See Figure 2).

In a **write operation**, the diodes at crosspoints are turned on or off by applying a large potential between one or more pairs of orthogonal NWs by addressing (giving low resistance to) one or more NWs in each dimension. Both ends of the NWs are maintained at the same potential. The polarity of the potential determines the state of a crosspoint and the value written.

In a **read operation**, a smaller voltage is used, allowing the decoder to detect the state of crosspoints. In a read operation each NW is disconnected from one of its ohmic contacts. Current will either flow or not flow through a crosspoint, depending on its state. The amount of current reveals the resistive state of the crosspoints, and thus the value being stored.

Both read and write operations require that the NWs being addressed have a significantly lower resistance than the other NWs in the same contact group. This requirement is formalized at the beginning of Section III.

## II. DECODING TECHNOLOGIES

In this section we briefly review three types of NW decoder. Each type of decoder can itself be manufactured in multiple

Fig. 1. A crossbar formed from two orthogonal sets of NWs with programmable molecules (PMs) at the crosspoints defined by intersecting NWs. NWs are divided into contact groups connected to pairs of OCs. To activate a NW in one dimension, a contact group is activated and MWs are used to deactivate all but one NW in that group. Data is stored at a crosspoint by applying a large electric field across it. Data is sensed with a smaller field.

Fig. 2. A crossbar-based memory in which OCs and MWs read and write data to programmable molecules at crosspoints. In a read operation an OC at each end of a NW is disconnected from ground. Current flows through any conducting NW crosspoints that are addressed by MWs. The amount of current reveals the value stored at the crosspoints. In a write operation, NWs along each dimension apply a larger electric field across their crosspoints. The direction of the field determines the value stored at the crosspoints.

ways. As shown in Section III, however, all three decoders can be model in a unified way. Using this model, in Section IV we analyze the RCD. In Section V we estimate the amount of area the RCD requires.

#### A. The Encoded NW Decoder

The **encoded NW decoder** works with two kinds of NWs, modulation-doped NWs [8], [10], NWs with sequences of lightly and heavily doped regions, and radially encoded NWs [16], NWs with removable shells. In both cases NWs are prepared externally and then deposited onto a chip using fluidic methods that align the NWs in parallel. These methods, however, do not guarantee end-to-end registration of NWs.

To explain the behavior of the encoded NW decoder on modulation-doped NWs, assume that lightly doped regions

are aligned with MWs. The junction formed by a lightly doped region and a MW forms a field effect transistor (FET). The application of an immobilizing electric field to a MW causes the resistance of the junction to become high. A NW is addressed by applying fields to all MWs that do not significantly increase its resistance. If doping sequences are properly chosen, only one NW type will become nonconducting. (See Figures 1 and 2.) In practice, lightly doped NW regions will not align perfectly with MWs. Consequently, MW control of NW junctions can be ambiguous. Several strategies to relate external binary addresses to doping patterns have been studied [9].

The encoded NW decoder also works with radially encoded NWs, that is, NWs that have shells composed of differentially etchable NWs [16]. There are several ways to control these NWs with MWs. The simplest method uses one MW for each type of NW. If NWs have *s* shells, a sequence of *s* materials can etched away in the space reserved for a MW. This process exposes the core of NWs of the given type but leaves at least one shell on NWs of different type. If all cores are lightly doped and shells are sufficiently thick, the MW controls only NWs with exposed cores. To address these NWs, all other MWs are activated. Radially encoded NWs do not suffer from misalignment but may require larger radii than modulation-doped NWs.

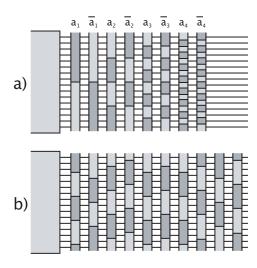

## B. The Masked-Based Decoder

The mask-based decoder [1] works with uniform NWs [14], [12], [3]. It assumes that lithograpically-defined high-K dielectric rectangles are deposited between NWs and MWs. These rectangles focus the field strength of MWs, thereby causing the lightly doped NWs sitting under them to have high resistance when an electric field is applied to the corresponding MW. If rectangles can be as small as the pitch of NWs, they can be used with  $M = 2\log_2 N$  MWs to cause all but one NW to have high resistance, as suggested in Figure 3a. Unfortunately, rectangles cannot be made as small as the pitch of NWs. Thus, it is proposed that many copies of the smallest lithographically-defined rectangles be deposited on a chip and that the natural randomness in their location that arises with their placement be used to provide control over NWs with high probability [1] (see Figure 3b). The number of MWs, M, needed to control N NWs is estimated to be at least six times the number required with an encoded NW decoder [15].

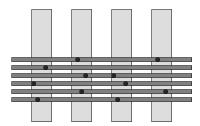

#### C. The Randomized-Contact Decoder

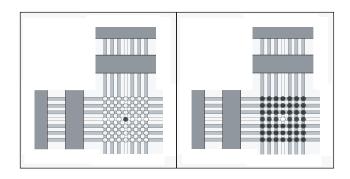

Williams and Kuekes introduced the randomized-contact decoder (RCD) [18], [11] for the addressing of undifferentiated nanowires (NWs). In an RCD random contacts are made between NWs and mesoscale wires (MWs) independently with some fixed probability. (See Figure 4.) If a contact is made between a NW and a MW, the junction acts as like a FET, that is, the application of an electric field to the MW causes a large increase in the resistance of the NW. If the number of MWs, M, is sufficiently large, the decoder will be able to address many individual NWs high probability.

Fig. 3. A masked-based NW decoder in which regions of high-K dielectric allow each MW to control a different subset of NW. If arbitrarily small high-K dielectric regions could be manufactured and placed with nanoscale precision,  $2 \log(N)$  MWs could be used to address each of N NWs. (See a).) Since this is not the case, many randomly shifted copies of the smallest manufacturable region can be used to gain control over individual NWs (See b).)

Fig. 4. A randomized-contact decoder in which random particle depostion causes each MW to control certain NWs.

A randomized-contact decoder is any decoder in which NW/MW connections can be modeled as independent random variables. In an RCD, a MW provides strong control over a NW with probability p, weak control with probability q and ambiguous control with probability 1 - (p + q). Because this third case is considered a manufacturing error, we do not assume that p + q = 1. In Section IV we bound the number of MWs M required to tolerate a given error rate.

There are a number of ways an RCD might be produced. One method would randomly deposit impurities (such as gold particles) onto undifferentiated NWs [18]. Another approach is to randomly deposit small regions of high-K dielectric, or alternatively, randomly etch holes in a low-K dielectric. An RCD can also be constructed from axially encoded NWs. If many sets of axially encoded NWs are produced with randomly placed lightly doped regions, each NW/MW junction can be treated as an independent random variable. As a result, analysis of RCDs provides bounds that apply to axial (and similarly radial) decoders.

Hogg et al [11] have explored the conditions under which most of the N NWs in an RCD can be controlled by a set of M MWs. They demonstrate through simulation that when M

passes a threshold, which is around 4.  $8 \log_2 N$ , the probability that most NWs are addressable grows rapidly as M increases. Their empirical study doesn't make explicit the dependence of M on N and the probability  $\epsilon$  of failing to having all NWs be addressable. Such a dependence is useful to both theory and design. We develop tight bounds for this purpose in Section IV.

## D. Stochastic Assembly and Address Translation Circuitry

Because NW decoders are assembled stochastically, there is a large amount of uncertainty regarding which MWs control which NWs. When assembled into a crossbar-based memory, external binary memory addresses must be mapped to NW crosspoints, that is, to pairs of orthogonal NWs.

Let each binary address E be split into high and low order bits,  $E_L$  and  $E_H$ , that separately address NWs in the two dimensions of the crossbar. An **address translation circuit** (ATC) is responsible for mapping  $E_L$  and  $E_H$  to a contact group and a subset of MWs within a group. Because the mapping of addresses to NWs varies from decoder to decoder, an ATC must contain some form of programmable storage. The greater the uncertainly regarding a decoder's configuration, the larger the storage space needed.

Most previous work on NW decoders has focused on the number of MWs required to control NWs. Although MWs are much wider than NWs, they are still relatively small. In an RCD, however, each NW/MW junction, corresponds to a bit of storage in address translation circuitry. As a result, these bits, which would be stored in mesoscale devices, collectively take up far more area than the NW/MW junctions.

As we show in Section V, it is not efficient to require that all NWs be individually addressable with high probability. The size of an ATC will vary based on the **NW addressing strategy** used. For example, we can require that a) all NWs in each simple decoder have a distinct address, or b) all NWs in almost all simple decoders have distinct addresses, or c) the total number of NWs with distinct addresses is sufficiently large. These are only a few of the possible addressing strategies.

#### III. MEMORY DECODER REQUIREMENTS

In Section IV, we bound the number of MWs required by RCDs to control crossbar-based memories. To derive these bounds, we first define the requirements that decoders must meet. The conditions we obtain in this section apply to other types of decoders as well.

## A. Nanowire Addressing

As explained in Section I, read/write operations are performed in a NW crossbar-based memory by employing an address decoder in each dimension of the memory. If each decoder addresses at least D disjoint sets of NWs, they collectively control  $D^2$  disjoint sets of NW crosspoints each of which can store a bit.

Since each of the two decoders is comprised of g contact groups,  $D = \sum_{i=1}^{g} D_i$ , where  $D_i$  is the number of disjoint sets of NWs that can be addressed within the ith contact group.

Let  $R_i$  be the resistance of NW  $n_i$ . When a decoder addresses a set S of NWs within a single contact group, each

Fig. 5. On the left, the crosspoint being read has a high resistance, but all other crosspoints have a low resistance. On the right, however, the crosspoint being read has a low resistance, but all other crosspoints have a high resistance. To correctly determine the state of the crosspoint, the amount of current flowing from one dimension of the crossbar to the other must be greater on the the right than the left.

NW in S has a low resistance, while the NWs not in S have a high resistance. In a write operation, every NW in S must have a much lower resistance than every NW not in S, that is,  $\max(R_i \mid \mathbf{n_i} \in \mathcal{S}) \ll \min(R_i \mid \mathbf{n_i} \notin \mathcal{S})$ . This ensures that the bits associated with NWs in S are written whereas those not in S are not written. A **read operation** requires that the combined resistance of all NWs in S,  $R_{IN}$ , be much less than the combined resistance of NWs not in S,  $R_{OUT}$ , that is  $1/R_{OUT} \ll 1/R_{IN}$ . The two extremes are illustrated in Figure 5. Since the resistance R of a set of n resistances,  $R_1, \ldots, R_n$ , placed in parallel satisfies  $1/R = 1/R_1 + \cdots + 1/R_n$ , this is equivalent to  $\sum_{n_i \notin S} 1/R_i \ll \sum_{n_i \in S} 1/R_i$ .

**Definition III.1** A set, S, of NWs is addressed if and only if a) every NW not in S has a resistance that is at least  $\alpha$ times that of every NW in S and b) the combined resistance of all NWs not in S is at least  $\alpha$  times that of the combined resistance of all NWs in S, where  $\alpha \gg 1$ .

Following the above analysis, if  $R_i \leq R_L$  when  $n_i \in \mathcal{S}$  and  $R_i \geq R_H$  when  $n_i \notin \mathcal{S}$ , the condition on writing is satisfied when  $R_H \ge \alpha R_L$  and that on reading is satisfied when  $R_H/(N-1)$  $|\mathcal{S}| \ge \alpha R_L/|\mathcal{S}|$ . This read condition is hardest to meet when  $|\mathcal{S}| = 1$  in which case  $R_H \geq \alpha (N-1) R_L$ . This is clearly stronger than the write condition  $R_H \ge \alpha R_L$ .

## B. Resistive and Ideal Models of Control

A NW decoder addresses a set of NWs by applying an electric field to a subset of the MWs. These MWs are said to be activated. The set of activated MWs is called an activation **pattern**. A particular activation pattern, a, is represented as a binary vector where  $a_i = 1$  if and only if the jth MW is activated. Each activated MW increases each NW's resistance by some amount (possibly 0). More formally, NWs behave as follows.

**Definition III.2** In the resistive model of NW control, each NW  $n_i$  has initial resistance  $\eta_i$  when no MWs are activated. Associated with each NW is a length-M vector of reals, or a real-valued nanowire codeword,  $r^i$ . The jth entry of  $r^i$ ,  $r^i_i$ , is the amount by which the jth MW increases the resistance of  $n_i$  when activated. When the decoder is supplied with a, the resistance of NW  $\mathbf{n_i}$  is  $\eta_i + \mathbf{a} \cdot \mathbf{r^i}$  where  $\mathbf{a} \cdot \mathbf{r^i}$  is the inner product of activation pattern a and codeword  $r^{i}$ .

When the jth MW provides strong control over NW  $n_i$ ,  $r_i^i$  is large.  $r_i^i$  is small when the jth MW provides weak control over  $n_i$ . In the ideal case each  $r_i^i$  is either 0 or  $\infty$  and a codeword is associated with each NW. Note that multiple NWs may have the same codeword.

**Definition III.3** In the ideal model of NW control, each NW,  $n_i$  is assigned a binary codeword,  $c^i$ , where  $c^i_i = 1$  if and only if  $r_i^i = \infty$ . For a particular activation pattern,  $a, a \cdot c^i > 0$  if and only if  $a \cdot r^i = \infty$ . A set S of NWs is addressed when  $\mathbf{a} \cdot \mathbf{c}^i = 0$  for NWs in S and  $\mathbf{a} \cdot \mathbf{c}^j = \infty$  for NWs not in S.

In either model of control, a set, S, of NWs is considered **addressable** if there is some activation pattern such that Sis addressed. Similarly, a particular NW  $n_i$  is individually **addressable** if there is an activation pattern such that  $\{n_i\}$  is addressed. A set of NWs is individually addressable if each of the NW codewords (there may be many copies of one codeword) is individually addressable.

Notice that in the ideal model of NW control, if a binary codeword is addressable, the NWs with that codeword are addressed by activation pattern  $a = c^i$ . Furthermore, if  $c^i$  is not addressable, there is some other codeword  $c^k$  such that for each j it is not true that  $c_i^i = 0$  and  $c_i^k = 1$ . This is the mathematical definition of implication; that is,  $c_i^k$  implies  $c_i^i$ . When this condition must hold for all values of j, we say that  $c^k$  implies  $c^i$ , and write  $c^k \Rightarrow c^i$ . The following is immediate.

Lemma III.1 In a simple NW decoder in the ideal model of control, a NW codeword  $c^i$  is addressable if and only if no other codeword that is present implies  $c^i$ . The decoder can address D disjoint sets of NWs if and only if D distinct NW codewords are addressable.

# C. Modeling Errors

As we have seen, if each  $r_i^i$  takes value  $r_{low} = 0$  or  $r_{high} =$  $\infty$ , each real-valued codeword can be mapped to a binary codeword, which are simple to work with. When  $r_{low}$  and  $r_{high}$ don't hold these extreme values we map  $\mathbf{r}^i$  to  $\mathbf{c}^i$  such that:

- $c^i_j = 0$  if  $r^i_j \le r_{low}$   $c^i_j = 1$  if  $r_{high} \le r^i_j$   $c^i_j = e$  if  $r_{low} \le r^i_j \le r_{high}$ , meaning that  $c^i_j$  is in error.

Our goal is to choose values for  $r_{low}$  and  $r_{high}$  so that a set S of NWs is addressed by an activation pattern a if the following conditions hold:

- for  $\mathbf{n}_i \in \mathcal{S}$ ,  $c_i^i = 0$  when  $a_i = 1$ ,

- for  $n_k \notin S$ , there exists j such that  $c_i^k = 1$  and  $a_i = 1$ .

Consider an activation pattern a that meets these two conditions. Let  $r_{base} = \max_i \eta_i$ . Observe that every NW in S has resistance at most  $R_L = r_{base} + (M-1)r_{low}$  because at most M-1 MWs are activated. Also, note that every NW not in S has resistance at least  $R_H = r_{high}$ . From Definition III.1 and the discussion that follows it is clear that S is addressed if  $R_H \geq \alpha(N-1)R_L$  or  $r_{high} \geq \alpha(N-1)(r_{base} + (M-1)r_{low})$ . To simplify the discussion, let  $r_{low} = cr_{base}$  for some constant c > 0. Then, S is addressed if

$$r_{high} \ge \alpha (N-1)(cM-c+1)r_{base}$$

Here  $\alpha$  is chosen to ensure that difference in current flowing in the presence of resistances  $r_{high}$  and  $r_{low}$  is measurable.

In the above model with errors we say that NW  $n_i$  is addressable if for each NW  $n_k$  there is at least one index (MW) j such that  $c_j^i = 0$  and  $c_j^k = 1$ . The ensures that  $c^i$  has low resistance while  $c^k$  has high resistance. When this condition fails,  $c^i$  may still be addressable but this cannot be guaranteed. We say that a **codeword**  $c^i$  fails to be addressable if there exists a codeword  $c^k$  such that the conditions  $c_j^i = 0$  and  $c_j^k = 1$  fail to be satisfied for some j. In this case, and by analogy with the ideal model, we say that codeword  $c^k$  possibly implies  $c^i$ , denoted  $c^k \stackrel{?}{\Rightarrow} c^i$ . If  $c^k \stackrel{?}{\Rightarrow} c^i$ , there is no guarantee that  $n_i$  can be addressed separately from  $n_k$ .

**Lemma III.2** In a simple decoder in the model with errors, a codeword,  $\mathbf{c}^i$ , is addressable if for no other codeword  $\mathbf{c}^k$  does  $\mathbf{c}^k \stackrel{?}{\Rightarrow} \mathbf{c}^i$ . The decoder can address D disjoint sets of NWs if and only if D distinct NW codewords are addressable.

If  $r_{high}$  is too low or  $r_{low}$  is too high to be realized using a particular decoding technology, NWs can still be addressed if we set  $r_{low} = cr_{base}$  and  $r_{high} = (\alpha/d)(N-1)(cM-c+1)r_{base}$  and require that each NW is addressed by activations  $\boldsymbol{a}$  that have a minimum of d > 1 1s.

It is possible that the RCD is realized with diodes instead of FETs. The decoder model with errors can also be used in this case to capture diodes with imperfect behavior.

## IV. ANALYSIS OF THE RCD

In an RCD, consider a simple decoder consisting of single contact group with N NWs and M MWs. As mentioned, we assume that NW/MW junctions are controlling (i.e.  $c_j^i = 1$ ) with probability p, noncontrolling (i.e.  $c_j^i = 0$ ) with probability q, and ambiguous (i.e.  $c_j^i$  is in error) with probability r = 1 - p - q. We also assume that these events are statistically independent and identically distributed.

We now bound  $N_a$ , the number of individually addressable NWs in each contact group in terms of M, the number of MWs. Recall that for a NW with codeword  $c^i$  to be individually addressable there must be no other codeword  $c^k$  such that  $c^k \stackrel{?}{\Rightarrow} c^i$  (see Lemma III.2).

We take two approaches to deriving bounds on M. First, in Theorem IV.1 we bound the expected value of  $N_a$ ,  $E[N_a]$ , and its variance,  $Var[N_a]$ . We then use Chebyshev's Inequality to derive a lower bound on M such that the total number of individually addressable wires across all g contact groups is close to gN with probability  $1 - \epsilon$ . Second, in Theorem IV.2, we use the principle of inclusion-exclusion to derive upper and lower bounds on M such that all NWs in all (or almost all) contact groups are independently addressable.

## A. Bounds Using Expectation and Variance

We develop bounds on the mean and variance in the number of individually addressable NWs. We use these to bound the probability that NWs in a compound RCD will be addressable with high probability. Proofs are in the Appendix.

**Theorem IV.1** In an RCD, let  $N_a$  be the number of independently addressable NWs in a contact group with N NWs and M MWs.  $N(1-N(1-pq)^M) \le E[N_a] \le N(1-(1-pq)^M)$  and  $Var[N_a] < E[N_a](N-E[N_a]) \le N^3(1-(1-pq)^M)(1-pq)^M$ .

**Corollary IV.1** Let N' = Ng be the total number of NWs contained in the g contact groups of a RCD, and let  $N'_a$  be the number of those NWs that are individually addressable. Then,  $N'(1 - (N'/g)(1 - pq)^M) \le E[N'_a] \le N'(1 - (1 - pq)^M)$  and  $Var[N'_a] < g(N'/g)^3(1 - (1 - pq)^M)(1 - pq)^M$ .

*Proof:* Since the numbers of individually addressable NW codewords in each contact group (which has N NWs) are independently and identically distributed,  $E[N'_a] = gE[N_a]$  and  $Var[N'_a] = gVar[N_a]$ . Substituting the bounds from Theorem IV.1 yields the desired result.

Chebyshev's Inequality is given below

$$P\left(|x - E[x]| \ge k\sqrt{Var[x]}\right) \le 1/k^2$$

where x is a random variable with mean E[x] and variance Var[x]. We use it to bound the probability that  $N'_a$  individually addressable NWs occur over g contact groups.

**Lemma IV.1** Let  $\alpha = 16\epsilon^{-1}/g$ . Then, an RCD with g contact groups and a total of N' NWs has at least  $(3N'/4)(1+\alpha)/(2+\alpha)$ ) individually addressable NWs with probability at least  $1-\epsilon$  if  $M > \ln \left(N'(2+\alpha)/g\right)/(-\ln(1-pq))$ .

Consider the case of N' = 1,600, g = 200 (there are 8 NWs per contact group),  $\epsilon = .01$ , and p = q = 1/2, all practical parameters. Then, the RCD has at least 1,080 individually addressable NWs, a very significant fraction of the NWs, when M > 16, a very modest number of MWs.

If errors occur, that is, when p + q < 1, the effect on the bound on M is to increase it. For example, if pq = .2 rather than pq = .25 in the error-free case, then M is larger by a factor of  $\ln(4/3)/\ln(5/4) = 1.29$ . If pq = .1, the factor is  $\ln(4/3)/\ln(10/9) = 2.73$ .

## B. Bounds Using Inclusion/Exclusion

We now derive bounds on the probability that a simple RCD fails to address all NWs. They are used to derive bounds on the number of MWs needed to establish an upper bound on the failure probability. Proofs are in the Appendix.

**Theorem IV.2** Let  $\Gamma$  be the probability of failing to control all N NWs using M MWs in a simple randomized-contact decoder when controlling and non-controlling contacts occur between NWs and MWs with probability p and q, respectively. An error occurs in a NW/MW junction with probability r = 1 - (p + q). Then,  $\Gamma$  satisfies the following bounds

$$Q(1 - Q/2) - \Delta \le \Gamma \le Q \tag{1}$$

where  $Q = N(N-1)\mu_1^M$  and  $\Delta = 2N(N-1)(N-2)$   $\left(\mu_3^M + \mu_5^M - 2\mu_1^{2M}\right)$  and  $\mu_1 = (1-pq)$ ,  $\mu_3 = (1-pq(p+2q))$ , and  $\mu_5 = (1-pq(2p+q))$ .

This theorem implies upper and lower bounds on M in terms of N and  $\Gamma$ . For the cases examined below when p=q and  $\Gamma$  is small, these bounds are exact. Slightly weaker but simple bounds are given below.

**Corollary IV.2** Consider a simple RCD that has N NWs and M MWs in which NW/MW intersections are controlling and non-controlling with probability p and q, respectively. The minimum value of M such that all NWs are addressable with probability  $1 - \epsilon$  satisfies the following.

$$\frac{\ln(N(N-1)/2\epsilon)}{-\ln(1-pq)} \le M \le \frac{\ln(N(N-1)/\epsilon)}{-\ln(1-pq)}$$

Here the lower bound holds only when  $M \ge \max(\min(p^2q, pq^2)^{-1}, \ln(10N(N-1))/(-\ln(1-pq)).$

*Proof:* The upper bound follows from (1). For the lower bound, assume  $Q \le 0.1$ , which implies that  $M \ge \ln(10N(N-1))/(-\ln \mu_1)$ . In  $\Delta$  drop the last term and replace  $\mu_3^M + \mu_5^M$  by  $2 \max(\mu_3, \mu_5)^M$ . Since  $\mu_3 = \mu_1 - pq^2$  and  $\mu_5 = \mu_1 - p^2q$ ,  $\max(\mu_3, \mu_5) = \mu_1(1 - \min(pq^2, p^2q)/\mu_1)$ . The lower bound on Γ becomes Γ ≥  $Q(.95 - 4N(1 - \min(pq^2, p^2q)/\mu_1)^M$ . Using the inequality  $(1 - x)^n \le 1 - nx$ , the lower bound is at least Q/2 if  $M \ge (1 - .45/4N)(1 - pq)/\min(p^2q, pq^2)$ . A stronger but more succinct condition is  $M \ge 1/\min(p^2q, pq^2)$ . ■

**Corollary IV.3** In a compound randomized-contact decoder with N' NWs divided into g contact groups, all N' are independently addressable with probability  $(1 - \epsilon)$  if  $M \ge \ln(N'((N'/g) - 1)/\epsilon)/(-\ln(1 - pq))$ .

*Proof:* Let  $\delta$  be the probability of failure of all NWs in a contact group to be individually addressable. Then, the probability that one or more contact groups fails to have all its NWs be individually addressable is at most  $g\delta$ . If  $g\delta \le \epsilon$ , the probability that all N' NWs are addressable is at least  $1 - \epsilon$ . We use the lower on M given in Corollary IV.2 when N is replaced by N'/g and  $\epsilon$  by  $\epsilon/g$ .

When N' = 1,600, g = 200 and  $M \ge 49$ , all N' NWs will be individually addressable with probability 0.99 or better. In fact, evaluating Theorem IV.2 numerically shows this threshold value of M to be exact.

This result can be improved if we don't require that in each contact group all NWs be individually addressable. We illustrate this with an example. Corollary IV.2 says that a failure rate of at most  $\epsilon=.01$  can be achieved with a simple RCD when p=q=.5 and N=8 if  $M\ge 30$ . (As above, this threshold value of M is exact.) If all N NWs in a particular contact group are individually addressable with probability  $1-\epsilon$ , since each simple RCD is formed with statistical independence, the probability that f or fewer contact groups fail to have all NWs addressable is  $\phi(\epsilon,f,g)=\sum_{i=0}^f {g \choose i} \epsilon^i (1-\epsilon)^{g-i}$ . Let  $\epsilon=.01$ , g=133 and f=5. Because  $\phi(.01,5,133)\ge.99$ , at least 128 of g=133 contact groups have all NWs addressable with probability 0.99.

In summary, when M = 30, g = 133, and N = 8\*133 = 1064,  $N'_a = 8*128 = 1,024$  NWs will be individually addressable with probability 0.99.

As explained at the end of Section IV-A, when errors can occur, that is, when  $p+q \le 1$ , the effect on the number of MWs needed to achieve a desired level of performance is small.

#### V. Addressing Strategies

We now use the bounds on M to estimate the total amount of area required for a crossbar-based memory that uses RCDs. As explained at the end of Section II, this area estimate depends not just on the number of MWs used but also on the size of an ATC. In this section we consider three addressing strategies, that is, ways of using an ATC to map an external binary address E of b = |E| bits to an internal NW address consisting of a contact group  $\sigma$  and an activation pattern a on M MWs.

All Wires Addressable: Here we choose M so that, with probability  $(1 - \epsilon)$ , all NWs in every contact group are individually addressable. If we assume that the number of NWs in each contact group is  $2^k$ , we can simply use the first b-k bits of E to select  $\sigma$ . This fixed mapping does not depend on the particular NW codewords that are present, although the mapping of E to E does. To execute the second mapping, the ATC can store each NW codeword that is present in a lookup table. This requires  $N_A'M$  bits of storage.

**Take What You Get:** Here we choose M so that almost all NWs are individually addressable. In this case, some contact groups may have all NWs addressable, but some will not. Since the number of addressable NWs per contact group varies, we can no longer map fixed blocks of binary memory addresses to a particular contact group. Instead, we store a value of  $\sigma$  and a for each addressable NW. This requires  $N'_4(\log g + M)$  bits.

## A. Area Estimate

To estimate the total area,  $A_T$ , required to produce a crossbar memory using each of the three strategies, we use approach of [9] and write:

$$A_T \approx 2\chi\beta + 2\lambda_{meso}^2 g \log_2 g + (\lambda_{meso} M + \lambda_{nano} N')^2$$

Here  $\lambda_{meso}$  and  $\lambda_{nano}$  denote the pitch of MWs and NWs respectively,  $\chi$  denotes the area of a mesoscale memory cell, and  $\beta$  denotes the number bits stored in an ATC for each of the two decoders. Thus,  $2\chi\beta$  is approximates the amount of space required to store the  $2\beta$  bits required by the ATCs in the dimensions of the crossbar,  $2\lambda_{meso}^2 g \log_2 g$  approximates the area required to implement a standard demultiplexer used by an ATC to activate contact groups, and  $(\lambda_{meso}M + \lambda_{nano}N')^2$  approximates the area used by the NW crossbar itself along with the M MWs along its periphery in each dimension.

## B. Comparison of Strategies

To compare the three addressing strategies, we estimate their area when used to produce a memory with a given storage capacity. In our comparison, we fix  $\epsilon$ , their probability of failure, and N'/g, the number of NWs per contact group. Given these values, we would ideally like to also fix  $N'_a$ , the number of addressable NWs along each dimension of the crossbar, then estimate  $A_T$  for all three strategies. Unfortunately, for a given strategy, it is difficult to choose M and N' to yield an exact value for  $N'_a$ , but in all three cases we show that about 1,000 NWs are addressable on each dimension of a crossbar.

To compare the strategies, we consider the case when p = q = 1/2 and use the numerical results given above.

#### • All Wires Addressable:

Here M=47, g=128, and  $N'=N'_a=1024$  with probability at least .99. The ATC requires  $\beta=N'_aM=47,990$  bits. This gives

$$A_T \approx 95,982\chi + \lambda_{meso}^2 1,792 + (\lambda_{meso} 49 + \lambda_{nano} 1,600)^2$$

# • All Wires Almost Always Addressable:

Here M = 30, g = 133, and N' = 1,064 yields  $N'_a = 1,024$  with probability at least .99. The ATC requires  $\beta = g \log g + N'_A M = 31,658$  bits. This gives

$$A_T \approx 63,316\chi + 1,877\lambda_{meso}^2 + +(\lambda_{meso}30 + \lambda_{nano}1,024)^2$$

## • Take What You Get:

Here M = 16, g = 200 and N' = 1,600, yields  $N'_a$  of 1,080 with probability at least .99. The ATC requires  $\beta = N'_a(\log g + M) = 25,535bits$ . This gives

$$A_T \approx 51,070\chi + 3,058\lambda_{meso}^2 + (\lambda_{meso}16 + \lambda_{nano}1,600)^2$$

Since the parameter  $\chi$ , the area of a mesoscale memory unit, is many times the other parameters, in particular  $\lambda_{meso}^2$ , the last strategy is the best.

#### VI. CONCLUSION

As we have demonstrated, a stochastically assembled NW decoder can be used to control a large number of NWs using a small number of MWs. When NW/MW control is resistive, we have provided a general decoder model that explains the requirements a decoder must meet, as well as how the decoder can function in the presence of errors.

We have applied our model to the randomized-contact decoder and given tight (in some cases exact) bounds on the number of MWs required to control a large number of NWs under various addressing strategies. We have also explained the significance of ATCs when estimating the area required for a crossbar based memory. By using multiple bounds on the number of MWs, we have illustrated that the size of the ATC for a memory is significantly reduced when we relax the requirement that all NWs be addressable.

# APPENDIX

**Theorem IV.1** In an RCD, let  $N_a$  be the number of independently addressable NWs in a contact group with N NWs and M MWs.  $N(1-N(1-pq)^M) \le E[N_a] \le N(1-(1-pq)^M)$  and  $Var[N_a] < E[N_a](N-E[N_a]) \le N^3(1-(1-pq)^M)(1-pq)^M$ .

*Proof:* Let  $x_i = 1$  if NW  $n_i$  is independently addressable and 0 otherwise. Since  $N_a = \sum_{i=1}^N x_i$ ,  $E[N_a] = \sum_{i=1}^N E[x_i]$ . Also, since the  $\{x_i\}$  are identically distributed 0-1 random variables,  $E[N_a] = NE[x_1] = NP(x_1 = 1)$ .

Let  $E_{k,i}$  be the event that  $c^k \stackrel{?}{\Rightarrow} c^i$ .  $P(x_1 = 1) = 1 - P(x_1 = 0) = 1 - P(E_{2,1} \cup E_{3,1} \cup \ldots \cup E_{N,1})$ . Since  $P(E_{2,1} \cup E_{3,1} \cup \ldots \cup E_{N,1}) \le \sum_{k=2}^{N} P(E_{k,1})$  and  $P(E_{2,1}) = P(E_{3,1}) = \ldots = P(E_{N,1})$ ,  $P(x_1 = 1) \ge 1 - NP(E_{2,1})$ .

$c^2 \not\stackrel{?}{\Rightarrow} c^1$  if there is no  $1 \le j \le M$  such that  $c_j^i = 0$  and  $c_j^k = 1$ , thus  $P(E_{2,1}) = (1 - pq)^M$  and  $P(x_1 = 1) \ge 1 - N(1 - pq)^M$ .

Let  $E[N_a^L] = N - N^2 (1 - pq)^M$ . Then,  $E[N_a] \ge E[N_a^L]$ . Let  $E[N_a^H] = N(1 - (1 - pq)^M)$ . Because  $P(E_{2,1} \cup E_{3,1} \cup \ldots \cup E_{N,1}) \ge P(E_{2,1})$ ,  $E[N_a] \le E[N_a^H]$ .

To bound  $Var[N_a] = E[N_a^2] - E[N_a]^2$ , we first bound  $E[N_a^2]$ .  $N_a^2 = (\sum_{i=1}^N x_i)^2 = \sum_{i=1}^N \sum_{k \neq i} x_i x_k + \sum_{i=1}^N x_i^2$ , and since all pairs  $(x_i, x_k)$  are identically distributed, and  $x_i^2 = x_i$ ,  $E[N_a^2] = N(N - 1)P(x_1 = x_2 = 1) + E[N_a]$ .

$P(x_1 = x_2 = 1) < P(x_1 = 1)$ , so  $E[N_a^2] < N(N-1)P(x_1 = 1) + E[N_a]$ , and  $NP(x_1 = 1) = E[N_a]$ , which gives  $E[N_a^2] < (N-1)E[N_a] + E[N_a] = NE[N_a]$ . Substituting back in to  $Var[N_a] = E[N_a^2] - E[N_a]^2$  gives  $Var[N_a] < NE[N_a] - E[N_a]^2 = E[N_a](N-E[N_a])$ . Applying the bounds on  $E[N_a]$ ,  $Var[N_a] < E[N_a^H](N-E[N_a^L]) = N^3(1 - (1 - pq)^M)(1 - pq)^M$ .

**Lemma IV.1** Let  $\alpha = 16\epsilon^{-1}/g$ . Then, an RCD with g contact groups and a total of N' NWs has at least  $(3N'/4)(1+\alpha)/(2+\alpha)$ ) individually addressable NWs with probability at least  $1-\epsilon$  if  $M \ge \ln \left(N'(2+\alpha)/g\right)/(-\ln(1-pq))$ .

*Proof:* We use Chebyshev's Inequality and Corollary IV.1. The probability  $P\left(N_a' \leq E[N_a'] - k\sqrt{Var[N_a']}\right)$  is bounded above by  $P\left(|N_a' - E[N_a']| \geq k\sqrt{Var[x]}\right) \leq 1/k^2$ . Thus,  $N_a' \geq E[N_a'] - k\sqrt{Var[N_a']}$  with probability at least  $1 - 1/k^2$ . If we replace  $E[N_a']$  by its lower bound and  $Var[N_a']$  by its upper bound, the probability is at least as large. The combined lower bound is  $N_L = N'(1 - (N'/g)\beta) - (k/g^{1/2})N'^{3/2}(1 - \beta)^{1/2}\beta^{1/2}$  where  $\beta = (1 - pq)^M$  and  $k = \epsilon^{-1/2}$ .

We choose  $\beta$  so that  $N_L$  be at least  $(3N'/4)(1-(N'/g)\beta)$ . Then,  $\beta$  satisfies  $1+b\beta+a\beta^2\geq 0$  where  $\alpha=16\epsilon^{-1}/g$ ,  $b=-(N'/g)(2+\alpha)$  and  $a=(N'/g)((N'/g)+\alpha)$ . Because  $\beta$  is positive, it satisfies the inequality  $\beta\geq -(b/(2a))(1-\sqrt{1-(4a/b^2)})$ . Since  $\beta=(1-pq)^M$  is a decreasing function of M, if we replace its lower bound by a smaller quantity this increases the value of M needed to achieve the indicated reliability bound. Using the inequality  $\sqrt{1-x}\leq 1-x/2$ , provides the bound  $\beta\geq 1/b=1/\left((N'/g)(2+\alpha)\right)$  and implies that  $M\geq \ln\left(N'(2+\alpha)/g\right)/(-\ln(1-pq))$ .

Under these conditions the lower bound on the number of addressable NWs is  $(3N'/4)(1 - (N'/g)(1 - pq)^M) \ge (3N'/4)(1 + \alpha)/(2 + \alpha))$ .

**Theorem IV.2** Let  $\Gamma$  be the probability of failing to control all N NWs using M MWs in the RCD when controlling and non-controlling contacts occur between NWs and MWs with probability p and q, respectively. An error occurs in a NW/MW junction with probability r = 1 - (p + q). Then,  $\Gamma$  satisfies the following bounds

$$Q(1 - Q/2) - \Delta \le \Gamma \le Q$$

where  $Q = N(N-1)\mu_1^M$  and  $\Delta = 2N(N-1)(N-2)$   $(\mu_3^M + \mu_5^M - 2\mu_1^{2M})$  and  $\mu_1 = (1-pq)$ ,  $\mu_3 = (1-pq(p+2q))$ , and  $\mu_5 = (1-pq(2p+q))$ .

*Proof:* The principle of inclusion-exclusion states that  $P(E_1 \cup E_0 \cup \ldots \cup E_n) \leq \sum_{i=1}^n P(E_i)$  and  $\sum_{i=1}^n P(E_i) - 1/2 \sum_{i \neq j} P(E_i \cap E_j) \leq P(E_1 \cup E_0 \cup \ldots \cup E_n)$ .

Let  $E_{a,b}$  (where  $a \neq b$ ) be the event that  $\mathbf{c}^a \stackrel{?}{\Rightarrow} \mathbf{c}^b$ . By Lemma III.2, we know that all NWs are independently addressable if no event  $E_{a,b}$  occurs. The probability that not all NWs are individually addressable,  $\Gamma$ , satisfies  $\Gamma = P(\bigcup_{(a,b)} E_{a,b})$ . We use inclusion-exclusion to bound  $\Gamma$ .

As established in the proof of Theorem IV.1,  $P(E_{a,b}) = \mu_1^M$  where  $\mu_1 = (1 - pq)$ . Let  $Q = \sum_{a \neq b} P(E_{a,b})$ . Since a and b can both take values from 1 to N,  $Q = N(N-1)\mu_1^M$ . We must now bound  $\sum_{(a,b)\neq(c,d)} P(E_{a,b}\cap E_{c,d})$ . Here  $1 \leq a,b,c,d \leq N$  provided that  $(a,b)\neq(c,d)$ , i.e., either  $a\neq b$  or  $c\neq d$  or both.

In case (1), a, b, c and d are all different. There are N(N-1)(N-2)(N-3) ways of selecting them. Since  $E_{a,b}$  and  $E_{c,d}$  are independent,  $P(E_{a,b} \cap E_{c,d}) = P(E_{a,b})P(E_{c,d}) = \mu_1^{2M}$ .

To compute  $P(E_{a,b} \cap E_{c,d})$ , we consider 3 cases:

In case (2), two of the four variables are equal. Here either a = c, a = d, b = c or b = d. As stated earlier, we do not allow a = b or c = d. There are N(N - 1)(N - 2) ways to choose indices in each case. These cases are considered below.

In case (3), there are only two different values for a, b, c, and d. Since  $(a,b) \neq (c,d)$ , a=d and b=c, which can occur in N(N-1) ways. Here  $P(E_{a,b} \cap E_{c,d}) = P(E_{a,b} \cap E_{b,a})$ , which is the probability that, for no j is  $c_j^a = 0$  and  $c_j^b = 1$ , or  $c_j^a = 1$  and  $c_j^b = 0$ . So  $P(E_{a,b} \cap E_{b,a}) = \mu_2^M$  where  $\mu_2 = (1-2pq)$ .

Returning to case 2, we have four subcases to consider.

Let  $F_{a,b}(m)$  be the event that  $c_m^a = 0$  and  $c_m^b = 1$ . Let  $E_{a,b}(m)$  be the complement of  $F_{a,b}(m)$ . Since the probability of  $F_{a,b}(m)$  is pq, it follows that the probability of event  $E_{a,b}(m)$  is  $P(E_{a,b}(m)) = 1 - pq$ . Since the event  $E_{a,b}$  is  $\prod_m E_{a,b}(m)$ ,  $P(E_{a,b}) = \mu_1^M$ .

- 1)  $n_a = n_c$ .  $F_{a,b}(m) \cup F_{a,d}(m)$  occurs only if  $(c_{a,m}, c_{b,m}, c_{d,m})$  assumes the value (0, 1, 0), (0, 1, 1), or (0, 0, 1). Thus,  $P(F_{a,b}(m) \cup F_{a,d}(m)) = pq(p+2q)$  and  $P(E_{a,b} \cap E_{c,d}) = \mu_3^M$  where  $\mu_3 = (1 pq(p+2q))$ .

- 2)  $n_a = n_d$ . Thus,  $F_{a,b}(m) \cup F_{c,a}(m)$  occurs if  $(c_{a,m}, c_{b,m}, c_{c,m})$  assumes the value (0, 1, 0), (0, 1, 1), (1, 1, 0), or (1, 0, 0). Thus,  $P(F_{a,b}(m) \cup F_{c,a}(m)) = 2pq(p+q)$  and  $P(E_{a,b}) \cap E_{c,a} = \mu_4^M$  where  $\mu_4 = (1 2pq(p+q))$ .

- 3)  $n_b = n_c$ . Thus,  $F_{a,b}(m) \cup F_{b,d}(m)$  occurs if  $(c_{a,m}, c_{b,m}, c_{d,m})$  assumes the value (0, 1, 0), (0, 1, 1), (0, 0, 1), or (1, 0, 1). Thus,  $P(F_{a,b}(m) \cup F_{c,b}(m)) = 2pq(p+q)$  and  $P(E_{a,b}) \cap E_{b,d} = \mu_4^M$ .

- 4)  $n_b = n_d$ . Thus,  $F_{a,b}(m) \cup F_{c,b}(m)$  occurs if  $(c_{a,m}, c_{b,m}, c_{c,m})$  assumes the value (0, 1, 0), (0, 1, 1), or (1, 1, 0). Thus,  $P(F_{a,b}(m) \cup F_{c,b}(m)) = pq(2p+q)$  and  $P(E_{a,b}) \cap E_{c,a} = \mu_5^M$  where  $\mu_5 = (1 pq(2p+q))$ .

Let  $D = \sum_{(a,b) \neq (c,d)} P(E_{a,b} \cap E_{c,d})$ . Then,

$$D/(N(N-1)) = (N-2)(N-3)\mu_1^{2M} + \mu_2^M + (N-2)(\mu_3^M + 2\mu_4^M + \mu_5^M)$$

where  $\mu_1 = (1 - pq)$ ,  $\mu_2 = (1 - 2pq)$ ,  $\mu_3 = (1 - pq(p + 2q))$ ,  $\mu_4 = (1 - 2pq(p+q))$ , and  $\mu_5 = (1 - pq(2p+q))$ . The behavior of D is dominated by the largest term  $\mu_i^M$ . Note that  $\mu_2 \leq \mu_1^2$  and  $\mu_4 \leq \min(\mu_3, \mu_5) \leq (\mu_3 + \mu_5)/2$ . It follows that  $(N-2)(N-3)\mu_1^{2M} + \mu_2^M \leq N(N-1)\mu_1^{2M}$  and  $(\mu_3^M + 2\mu_4^M + \mu_5^M) \leq 2(\mu_3^M + \mu_5^M)$ . Thus, D satisfies the following bound.

$$D \le Q^2 + 2N(N-1)(N-2)\left(\mu_3^M + \mu_5^M - 2\mu_1^{2M}\right)$$

The lower bound to  $\Gamma$  follows directly from the above.

#### REFERENCES

- R. Beckman, E. Johnston-Halperin, Y. Luo, J. E. Green, and J. R. Heath, "Bridging dimensions: Demultiplexing ultrahigh-density nanowire circuits," *Science*, vol. 310, pp. 465–468, 2005.

- [2] Y. Chen, G.-Y. Jung, D. A. A. Ohlberg, X. Li, D. R. Stewart, J. O. Jeppeson, K. A. Nielson, J. F. Stoddart, and R. S. Williams, "Nanoscale molecular-switch crossbar circuits," *Nanotechnology*, vol. 14, pp. 462–468, 2003.

- [3] S. Y. Chou, P. R. Krauss, and P. J. Renstrom, "Imprint lithography with 25-nanometer resolution," *Science*, vol. 272, pp. 85–87, 1996.

- [4] C. P. Collier, E. W. Wong, M. Belohradský, F. M. Raymo, J. F. Stoddart, P. J. Kuekes, R. S. Williams, and J. R. Heath, "Electronically configurable molecular-based logic gates," *Science*, vol. 285, pp. 391–394, 1999.

- [5] C. P. Collier, G. Mattersteig, E. W. Wong, Y. Luo, K. Beverly, J. Sampaio, F. Raymo, J. F. Stoddart, and J. R. Heath, "A [2]catenate-based solid state electronically reconfigurable switch," *Science*, vol. 290, pp. 1172–1175, 2000.

- [6] A. DeHon, "Nanowire-based programmable architectures," J. Emerg. Technol. Comput. Syst., vol. 1, no. 2, pp. 109–162, 2005.

- [7] A. DeHon, S. C. Goldstein, P. Kuekes, and P. Lincoln, "Nonphotolithographic nanoscale memory density prospects," *IEEE Transactions on Nanotechnology*, vol. 4, no. 2, pp. 215–228, 2005.

- [8] A. DeHon, P. Lincoln, and J. E. Savage, "Stochastic assembly of sublithographic nanoscale interfaces," *IEEE Transactions on Nanotech*nology, vol. 2, no. 3, pp. 165–174, 2003.

- [9] B. Gojman, E. Rachlin, and J. E. Savage, "Evaluation of design strategies for stochastically assembled nanoarray memories," *J. Emerg. Technol. Comput. Syst.*, vol. 1, no. 2, pp. 73–108, 2005.

- [10] —, "Decoding of stochastically assembled nanoarrays," in *Procs 2004 Int. Symp. on VLSI*, Lafayette, LA, Feb. 19-20, 2004.

- [11] T. Hogg, Y. Chen, and P. J. Kuekes, "Assembling nanoscale circuits with randomized connections," *IEEE Trans. Nanotechnology*, vol. 5, no. 2, pp. 110–122, 2006.

- [12] E. Johnston-Halperin, R. Beckman, Y. Luo, N. Melosh, J. Green, and J. Heath, "Fabrication of conducting silicon nanowire arrays," *J. Applied Physics Letters*, vol. 96, no. 10, pp. 5921–5923, 2004.

- [13] G. Y. Jung, S. Ganapathiappan, A. A. Ohlberg, L. Olynick, Y. Chen, W. M. Tong, and R. S. Williams, "Fabrication of a 34x34 crossbar structure at 50 nm half-pitch by UV-based nanoimprint lithography," *Nano Letters*, vol. 4, no. 7, pp. 1225–1229, 2004.

- [14] N. A. Melosh, A. Boukai, F. Diana, B. Gerardot, A. Badolato, P. M. Petroff, and J. R. Heath, "Ultrahigh-density nanowire lattices and circuits," *Science*, vol. 300, pp. 112–115, Apr. 4, 2003.

- [15] E. Rachlin, J. E. Savage, and B. Gojman, "Analysis of a mask-based nanowire decoder," in *Procs 2005 Int. Symp. on VLSI*, Tampa, FL, May 11-12, 2005.

- [16] J. E. Savage, E. Rachlin, A. DeHon, C. M. Lieber, and Y. Wu, "Radial addressing of nanowires," *J. Emerg. Technol. Comput. Syst.*, vol. 2, no. 2, pp. 129–154, 2006.

- [17] D. Whang, S. Jin, and C. M. Lieber, "Nanolithography using hierarchically assembled nanowire masks," *Nano Letters*, vol. 3, no. 7, pp. 951–954, 2003.

- [18] R. S. Williams and P. J. Kuekes, "Demultiplexer for a molecular wire crossbar network, US Patent Number 6,256,767," July 3, 2001.

- [19] Z. Zhong, D. Wang, Y. Cui, M. W. Bockrath, and C. M. Lieber, "Nanowire crossbar arrays as address decoders for integrated nanosystems," *Science*, vol. 302, pp. 1377–1379, 2003.